Table of Contents

Advertisement

Quick Links

M68060 User's Manual

Including the

MC68060,

MC68LC060,

and

MC68EC060

Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding

the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and

specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different

applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not

convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems

intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola

product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or

µ

unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims,

costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such

unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and

are

registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

© MOTOROLA, 1994

Advertisement

Chapters

Table of Contents

Summary of Contents for Motorola M68060

- Page 1 Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages.

- Page 2 Documentation Comments FAX 512-891-8593—Documentation Comments Only The Motorola High-End Technical Publications Department provides a fax number for you to submit any questions or comments about this document or how to order other documents. We welcome your suggestions for improving our documentation. Please do not fax technical questions.

- Page 3 CHINA , Beijing 86 505-2180 HYBRID COMPONENTS RESELLERS FINLAND , Helsinki 358-0-35161191 Elmo Semiconductor (818) 768-7400 Car Phone 358(49)211501 Minco Technology Labs Inc. (512) 834-2022 FRANCE , Paris/Vanves 33(1)40 955 900 Semi Dice Inc. (310) 594-4631 M68060 USER’S MANUAL MOTOROLA...

- Page 4 PREFACE The complete documentation package for the MC68060, MC68LC060, and MC68EC060 (collectively called M68060) consists of the M68060UM/AD, M68060 User’s Manual , and the M68000PM/AD, M68000 Family Programmer’s Reference Manual . The M68060 User’s Manual describes the capabilities, operation, and programming of the M68060 superscalar 32-bit microprocessors.

- Page 5 FP7–FP0—floating-point data registers 7–0 FSLW—fault status long word IEE—integer execute unit IFP—instruction fetch pipeline IFU—instruction fetch unit IPU—instruction pipe unit ISP—interrupt stack pointer ITTR—instruction transparent translation register IU—integer unit JTAG—Joint Test Action Group MMU—memory management unit MOTOROLA M68060 USER’S MANUAL...

- Page 6 MC68060 Acronym List MMUSR—memory management unit status register M68060SP—M68060 software package NANs—not-a-numbers NOP—no operation OEP—operand execution pipeline OPU—operand pipe unit PC—program counter PCR—processor configuration register PGI—page index field PI—pointer index field PLL—phase-locked loop pOEP—primary operand execution pipeline RI—root index field SFC—source function code...

-

Page 7: Table Of Contents

TABLE OF CONTENTS Section 1 Introduction Differences Among M68060 Family Members..........1-3 1.1.1 MC68LC060....................1-3 1.1.2 MC68EC060 ....................1-3 1.1.2.1 Address Translation Differences .............. 1-3 1.1.2.2 Instruction Differences ................1-3 Features......................1-4 Architecture....................1-4 Processor Overview..................1-5 1.4.1 Functional Blocks..................1-5 1.4.2... - Page 8 2.11.4 Test Data In (TDI)..................2-16 2.11.5 Test Data Out (TDO) ................2-16 2.11.6 Test Reset (TRST) ................... 2-16 2.12 Thermal Sensing Pins (THERM1, THERM0)..........2-16 2.13 Power Supply Connections................. 2-16 2.14 Signal Summary ..................2-16 M68060 USER’S MANUAL MOTOROLA...

- Page 9 Supervisor Only ..................4-22 4.2.6.3 Write Protect ................... 4-22 Address Translation Caches............... 4-24 Transparent Translation................4-27 Address Translation Summary..............4-28 RSTI and MDIS Effect on the MMU ............4-28 4.6.1 Effect of RSTI on the MMUs ..............4-28 MOTOROLA M68060 USER’S MANUAL...

- Page 10 Floating-Point Control Register (FPCR) ............. 6-3 6.1.2.1 Exception Enable Byte ................6-3 6.1.2.2 Mode Control Byte..................6-3 6.1.3 Floating-Point Status Register (FPSR)............6-4 6.1.3.1 Floating-Point Condition Code Byte ............6-5 6.1.3.2 Quotient Byte.................... 6-5 6.1.3.3 Exception Status Byte ................6-5 M68060 USER’S MANUAL MOTOROLA...

- Page 11 Bus Operation Bus Characteristics ..................7-1 Full-, Half-, and Quarter-Speed Bus Operation and BCLK ......7-3 Acknowledge Termination Ignore State Capability ........7-4 Bus Control Register..................7-4 Data Transfer Mechanism................7-5 Misaligned Operands ..................7-9 MOTOROLA M68060 USER’S MANUAL xiii...

- Page 12 Illegal Instruction and Unimplemented Instruction Exceptions ....8-8 8.2.5 Privilege Violation Exception ..............8-10 8.2.6 Trace Exception..................8-10 8.2.7 Format Error Exception ................8-11 8.2.8 Breakpoint Instruction Exception .............. 8-11 8.2.9 Interrupt Exception ................... 8-12 8.2.10 Reset Exception ..................8-14 M68060 USER’S MANUAL MOTOROLA...

- Page 13 Bypass Register ..................9-15 9.1.4 Restrictions ....................9-15 9.1.5 Disabling the IEEE 1149.1 Standard Operation ........9-15 9.1.6 Motorola MC68060 BSDL Description............9-17 Debug Pipe Control Mode................9-24 9.2.1 Debug Command Interface............... 9-25 9.2.2 Debug Pipe Control Mode Commands ............. 9-27 9.2.3...

- Page 14 Page and Descriptor Faults (Access Error Handler)......11-4 11.1.2.2.4 PTEST, MOVEC of MMUSR, and PLPA..........11-4 11.1.2.3 Context Switch Interrupt Handlers............11-5 11.1.2.4 Trace Handlers ..................11-5 11.1.2.5 I/O Device Driver Software ..............11-5 11.1.3 Precise Vs. Imprecise Exception Mode ............ 11-6 M68060 USER’S MANUAL MOTOROLA...

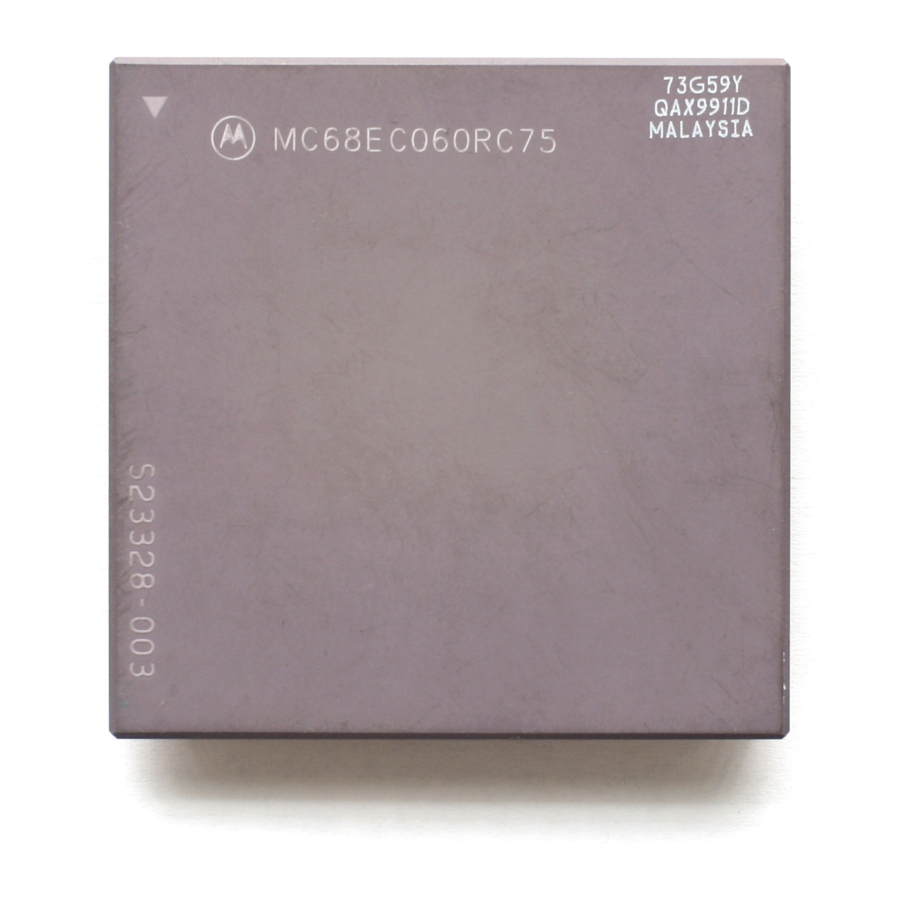

- Page 15 MC68060, MC68LC060, and MC68EC060 Pin Grid Array (RC Suffix) ..13-2 13.2.2 MC68060, MC68LC060, and MC68EC060 Quad Flat Pack (FE Suffix)... 13-3 13.3 Mechanical Data ..................13-4 Appendix A MC68LC060 Appendix B MC68EC060 Address Translation Differences..............B-1 Instruction Differences ..................B-1 MOTOROLA M68060 USER’S MANUAL xvii...

- Page 16 Instructions Not Recommended ...............C-26 Installation Notes ..................C-27 C.5.1 Installing the Library Modules..............C-27 C.5.2 Installing the Kernel Modules ..............C-27 C.5.3 Release Notes and Module Offset Assignments ........C-28 C.5.4 AESOP Electronic Bulletin Board .............C-29 Appendix D MC68060 Instructions xviii M68060 USER’S MANUAL MOTOROLA...

- Page 17 Caching Operation ..................... 5-3 Cache Control Register ..................5-5 Instruction Cache Line State Diagram.............. 5-16 Data Cache Line State Diagrams..............5-18 Floating-Point Unit Block Diagram ..............6-2 Floating-Point User Programming Model ............6-3 Floating-Point Control Register Format.............. 6-4 MOTOROLA M68060 USER’S MANUAL...

- Page 18 LPSTOP Broadcast Bus Cycle Timing, BG Negated ........7-42 7-34 LPSTOP Broadcast Bus Cycle Timing, BG Asserted ........7-43 7-35 Exiting LPSTOP Mode Flowchart..............7-44 7-36 Exiting LPSTOP Mode Timing Diagram............7-45 7-37 Word Write Access Bus Cycle Terminated with TEA Timing ......7-48 M68060 USER’S MANUAL MOTOROLA...

- Page 19 MC68060 Address Hold Time ................ 11-12 11-7 MC68060 Address Hold Time Fix ..............11-12 11-8 Simple CLK Generation.................. 11-14 11-9 Generic CLK Generation ................11-14 11-10 MC68040 BCLK to CLKEN Relationship............11-15 11-11 DRAM Timing Analysis................... 11-15 MOTOROLA M68060 USER’S MANUAL...

- Page 20 MUL Instruction Call Example................C-11 CMP2 Instruction Call Example ...............C-11 SNAN/OPERR Exception Handler Pseudo-Code ..........C-18 Disabled vs. Enabled Exception Actions............C-20 C-10 _mem_read Pseudo-Code ................C-23 C-11 Register Usage of {i,d}mem_{read,write}_{b,w,l} ..........C-25 C-12 Vector Table and M68060SP Relationship ............C-28 xxii M68060 USER’S MANUAL MOTOROLA...

- Page 21 Summary of Access Types vs. Bus Signal Encoding......... 7-9 Memory Alignment Influence on Noncachable and Writethrough Bus Cycles.................. 7-12 Interrupt Acknowledge Termination Summary ..........7-34 Termination Result Summary................7-46 MC68040-Arbitration Protocol Transition Conditions ........7-55 MOTOROLA M68060 USER’S MANUAL xxiii...

- Page 22 With Heat Sink, No Air Flow................11-18 11-2 With Heat Sink, with Air Flow ................. 11-18 11-3 No Heat Sink ....................11-19 11-4 Support Devices and Products............... 11-20 Call-Out Dispatch Table and Module Size ............C-4 FPU Comparison....................C-12 Unimplemented Instructions................C-13 xxiv M68060 USER’S MANUAL MOTOROLA...

- Page 23 Instructions Not Handled by the M68060SP ........... C-26 Files Provided in an M68060SP Release............C-27 M68000 Family Instruction Set and Processor Cross-Reference ..... D-1 M68000 Family Instruction Set................D-6 Exception Vector Assignments for the M68000 Family........D-10 MOTOROLA M68060 USER’S MANUAL...

- Page 24 List of Tables xxvi M68060 USER’S MANUAL MOTOROLA...

- Page 25 INTRODUCTION The superscalar MC68060 represents a new line of Motorola microprocessor products. The first generation of the M68060 product line consists of the MC68060, MC68LC060, and MC68EC060. All three microprocessors offer superscalar integer performance of over 100 MIPS at 66 MHz. The MC68060 comes fully equipped with both a floating-point unit (FPU) and a memory management unit (MMU) for high-performance embedded control and desk- top applications.

- Page 26 The functionality provided by the MC68060 makes it the ideal choice for a range of high-performance embedded applications and com- puting applications. With M68000 family code compatibility, the MC68060 provides a range of upgrade opportunities to virtually any existing MC68040 application. M68060 USER’S MANUAL MOTOROLA...

-

Page 27: Introduction

Introduction 1.1 DIFFERENCES AMONG M68060 FAMILY MEMBERS Because the functionality of individual M68060 family members are similar, this manual is organized so that the reader will take the following differences into account while reading the rest of this manual. Unless otherwise noted, all references to MC68060, with the excep- tion of the differences outlined below, will apply to the MC68060, MC68LC060, and MC68EC060. -

Page 28: 1.2 Features

OEPs perform in a lock-step mode of operation, the multiple instruction execution is per- formed simultaneously, but not out-of-order. The net effect is a software-invisible pipeline architecture capable of sustained execution rates of < 1 machine cycle per instruction of the M68000 instruction set. M68060 USER’S MANUAL MOTOROLA... -

Page 29: 1.4 Processor Overview

MHz to the pipelines, while the integer execute engines can support sustained transfer rates of 1.2 GBytes/sec. 1.4 PROCESSOR OVERVIEW The following paragraphs provide a general description of the MC68060. 1.4.1 Functional Blocks Figure 1-1 illustrates a simplified block diagram of the MC68060. MOTOROLA M68060 USER’S MANUAL... -

Page 30: Integer Unit

DECODE DATA FLOATING- POINT UNIT CALCULATE CALCULATE DATA CACHE FETCH FETCH FETCH CONTROLLER EXECUTE EXECUTE EXECUTE DATA DATA INTEGER UNIT CACHE CONTROL DATA MEMORY UNIT DATA AVAILABLE WRITE-BACK OPERAND DATA BUS Figure 1-1. MC68060 Block Diagram M68060 USER’S MANUAL MOTOROLA... -

Page 31: 1.4.2 Integer Unit

If a hit occurs in the branch cache, indicating a branch taken instruction, the current instruction stream is discarded and a new instruction stream is fetched starting at the location indicated by the branch cache. MOTOROLA M68060 USER’S MANUAL... -

Page 32: Floating-Point Unit

The FPU has been optimized for the most frequently used instructions and data types to pro- vide the highest possible performance. The FPU can also be disabled in software to reduce system power consumption. M68060 USER’S MANUAL MOTOROLA... -

Page 33: Memory Units

The parallelism inherent in the MC68060 also allows multiple instructions that do not require any external accesses to exe- MOTOROLA M68060 USER’S MANUAL... -

Page 34: Cache Organization

External condi- tions, such as interrupts and access errors, also cause exceptions. Exception processing ends when the first instruction of the exception handler begins to execute. 1-10 M68060 USER’S MANUAL MOTOROLA... -

Page 35: 1.6 Programming Model

S-bit, forcing the processor into the supervisor mode. To return to the user mode, a system routine must execute one of the following instructions: MOVE to SR, ANDI to SR, EORI to SR, ORI to SR, or RTE, which execute in the supervisor mode, MOTOROLA M68060 USER’S MANUAL 1-11... -

Page 36: Programming Model

INSTRUCTION TRANSPARENT TRANSLATION REGISTER 1 BUSCR BUS CONTROL REGISTER SUPERVISOR PROGRAMMING MODEL Figure 1-2. Programming Model Only system programmers can use the supervisor programming model to implement oper- ating system functions, I/O control, and memory management subsystems. This supervisor/ 1-12 M68060 USER’S MANUAL MOTOROLA... - Page 37 A floating-point status register (FPSR) con- tains a condition code byte, quotient byte, exception status byte, and accrued exception MOTOROLA M68060 USER’S MANUAL 1-13...

-

Page 38: Data Format Summary

The program counter indirect mode also has indexing and offset capa- bilities. This addressing mode is typically required to support position-independent software. Besides these addressing modes, the MC68060 provides index sizing and scaling features. 1-14 M68060 USER’S MANUAL MOTOROLA... -

Page 39: 1.9 Instruction Set Overview

Refer to Table 1-4 for notations used in Table 1-3. The left operand in the syntax is always the source operand, and the right operand is the destination operand. Refer to M68000PM/AD, M68000 Family Programmer’s Reference Manual, for details on instructions used by the MC68060. MOTOROLA M68060 USER’S MANUAL 1-15... -

Page 40: Instruction Set Summary

TRAP If Rn < LB or If Rn > UB CHK2 <ea>,Rn CHK2 then TRAP If supervisor state CINVL <caches>, (An) CINV then invalidate selected cache lines CINVP <caches>, (An) else TRAP CINVA <caches> 1-16 M68060 USER’S MANUAL MOTOROLA... - Page 41 Dn – 1 ˘ Dn FDBcc 2 if Dn ≠ –1 FDBcc Dn,<label> then PC + d n ˘ PC else execute next instruction FDIV.<fmt> <ea>,FPn FDIV.X FPm,FPn FPn ÷ Source ˘ FPn FDIV FrDIV.<fmt> <ea>,FPn FrDIV.X FPm,FPn MOTOROLA M68060 USER’S MANUAL 1-17...

- Page 42 SSP – 2 ˘ SSP; Vector Offset ˘ (SSP); SSP – 4 ˘ SSP; PC ˘ (SSP); ILLEGAL ILLEGAL SSp – 2 ˘ SSP; SR ˘ (SSP); Illegal Instruction Vector Address ˘ PC Destination Address ˘ PC JMP <ea> 1-18 M68060 USER’S MANUAL MOTOROLA...

- Page 43 NEGX <ea> None ~ Destination ˘ Destination NOT <ea> OR <ea>,Dn Source V Destination ˘ Destination OR Dn,<ea> Immediate Data V Destination ˘ Destination ORI #<data>,<ea> ORI to CCR Source V CCR ˘ CCR ORI #<data>,CCR MOTOROLA M68060 USER’S MANUAL 1-19...

- Page 44 Destination Tested ˘ Condition Codes TST <ea> UNLK An ˘ SP; (SP) ˘ An; SP + 4 ˘ SP UNLK An Source (Packed BCD) + adjustment ˘ Destination (Unpacked UNPACK –(Ax),–(Ay),#(adjustment) UNPK BCD) UNPACK Dx,Dy,#(adjustment) 1-20 M68060 USER’S MANUAL MOTOROLA...

-

Page 45: 1.10 Notational Conventions

Any Data Register n (example: D5 is data register 5) Dr, Dq Data register’s remainder or quotient of divide. Data register D7–D0, used during update. Dx, Dy Source and destination data registers, respectively. Any Memory Register n. MOTOROLA M68060 USER’S MANUAL 1-21... - Page 46 Register Codes General Case. Carry Bit in CCR Condition Codes from CCR Function Code Negative Bit in CCR Undefined, Reserved for Motorola Use. Overflow Bit in CCR Extend Bit in CCR Zero Bit in CCR — Not Affected or Applicable.

-

Page 47: Signal Description

Transfer in Progress Asserted for the duration of a bus cycle. Starting Termination Ac- knowledge Signal Sam- Indicates the MC68060 will begin sampling the termination acknowledge signals. pling Transfer Acknowledge Asserted to acknowledge a bus transfer. MOTOROLA M68060 USER’S MANUAL... - Page 48 Serial data output for the TAP. Test Reset TRST Provides an asynchronous reset of the TAP controller. Thermal Resistor Con- THERM1, Provides thermal sensing information. nections THERM0 V CC Power Supply Power supply. Ground Ground connection. M68060 USER’S MANUAL MOTOROLA...

-

Page 49: 2.1 Address And Control Signals

These three-state bidirectional signals provide the address of the first item of a bus transfer (except for interrupt acknowledge transfers) when the MC68060 is the bus master. When an alternate bus master is controlling the bus and asserts the SNOOP signal, the address sig- MOTOROLA M68060 USER’S MANUAL... -

Page 50: Cycle Long-Word Address (Cla)

Table 2-3 lists the encoding for normal (TTx = 00) and MOVE16 (TTx = 01) transfers, and Table 2-4 lists the encoding for alternate access transfers (TTx = 10). For interrupt acknowl- edge transfers, the TMx signals carry the interrupt level being acknowledged. For breakpoint M68060 USER’S MANUAL MOTOROLA... - Page 51 Signal Description acknowledge transfers and low-power stop broadcast cycles, the TMx signals are negated. When the MC68060 is not the bus master, the TMx signals are in a high-impedance state. MOTOROLA M68060 USER’S MANUAL...

-

Page 52: Transfer Line Number (Tln1, Tln0)

UPAx signals are defined by the logical values of the U1 and U0 bits in the ATC entry. If a given logical address is not mapped by the TTRs and if address translation is disabled, M68060 USER’S MANUAL MOTOROLA... -

Page 53: Read/Write (R/W)

(except in the case in which a retry termination is indicated on the last write of a read-modify-write sequence). When the MC68060 is not the bus master, the LOCKE signal is set to a high-impedance state. If the MC68060 relinquishes the bus while LOCKE is asserted, LOCKE will be negated MOTOROLA M68060 USER’S MANUAL... -

Page 54: Data Bus Byte Select Signals

The following signals provide control functions for bus cycles when the MC68060 is the bus master. Refer to Section 7 Bus Operation for detailed information about the relationship of the bus cycle control signals to bus operation. M68060 USER’S MANUAL MOTOROLA... - Page 55 TRA and TEA must be negated when TA is asserted. 2.5.2 Transfer Retry Acknowledge (TRA) For native-MC68060-style (non-MC68040-style) acknowledge termination, this input signal may be asserted by the current slave on the first transfer of a bus cycle to indicate the need MOTOROLA M68060 USER’S MANUAL...

- Page 56 Section 5 Caches provides information about the relationship of SNOOP to the caches, and Section 7 Bus Operation discusses the relationship of SNOOP to bus operation. 2-10 M68060 USER’S MANUAL MOTOROLA...

- Page 57 MC68060 may become the bus master. To properly maintain this internal state information, all masters on the bus must have their TS signals tied together and their BTT signals tied together so the MC68060 can keep track of TS-BTT pairs. MOTOROLA M68060 USER’S MANUAL 2-11...

- Page 58 (CINVA, CINVP, CINVL) are executed. The execution of one of the cache invalidate instruc- tions may invalidate entries even if the caches have been disabled with this signal. The assertion of CDIS does not affect snooping. Refer to Section 5 Caches for information about the caches. 2-12 M68060 USER’S MANUAL MOTOROLA...

- Page 59 (SR). Exter- nal devices (other bus masters) can use IPEND to predict processor operation on the next instruction boundaries. IPEND is not intended for use as an interrupt acknowledge to exter- MOTOROLA M68060 USER’S MANUAL 2-13...

- Page 60 CLK period per instruction and are mutually exclusive. In general, the PSTx bits indicate the following information: PST4 = Supervisor Mode PST3 = Branch Instruction PST2 = Taken Branch Instruction PST1, PST0 = Number of Instructions Completed that Cycle 2-14 M68060 USER’S MANUAL MOTOROLA...

- Page 61 This input signal is a qualifier for the MC68060 processor clock (CLK) and is provided to sup- port lower bus frequency MC68060 designs. The internal MC68060 bus interface controller will sample, assert, negate, or three-state signals (except for BB and TIP which can three- MOTOROLA M68060 USER’S MANUAL 2-15...

- Page 62 This input signal is decoded by the TAP controller and distinguishes the principal operations of the test support circuitry. TMS should be tied to V if it is not used and emulation mode is not to be used. 2-16 M68060 USER’S MANUAL MOTOROLA...

-

Page 63: 2.14 Signal Summary

Section 13 Ordering Information and Mechanical Data describes the groupings of the V and ground connections. 2.14 SIGNAL SUMMARY Table 2-8 provides a summary of the electrical characteristics of the MC68060 signals. MOTOROLA M68060 USER’S MANUAL 2-17... - Page 64 — Test Data Output Output High Three-Stated Test Reset TRST Input — — THERM1, Thermal Resistor Connections — — — — THERM0 V CC Power Supply Input — — — Ground Input — — — 2-18 M68060 USER’S MANUAL MOTOROLA...

-

Page 65: Mc68060 Integer Unit Pipeline

DATA FLOATING- POINT UNIT CALCULATE CALCULATE DATA CACHE FETCH FETCH FETCH CONTROLLER EXECUTE EXECUTE EXECUTE DATA DATA INTEGER UNIT CACHE CONTROL DATA MEMORY UNIT DATA AVAILABLE WRITE-BACK OPERAND DATA BUS Figure 3-1. MC68060 Integer Unit Pipeline MOTOROLA M68060 USER’S MANUAL... -

Page 66: Integer Unit User Programming Model

3.2.1.3 USER STACK POINTER (A7). A7 is used as a hardware stack pointer during implicit or explicit stacking for subroutine calls and exception handling. The register desig- nation A7 refers to the user stack pointer (USP) in the user programming model and to the M68060 USER’S MANUAL MOTOROLA... -

Page 67: Integer Unit Supervisor Programming Model

Thus, all application software is written to run in the user mode and migrates to the MC68060 from any M68000 platform without modification. SUPERVISOR STACK POINTER A7 (SSP) (CCR) STATUS REGISTER VECTOR BASE REGISTER ALTERNATE SOURCE AND DESTINATION FUNCTION CODE REGISTERS PROCESSOR CONFIGURATION REGISTER Figure 3-3. Integer Unit Supervisor Programming Model MOTOROLA M68060 USER’S MANUAL... - Page 68 3.2.2.3 VECTOR BASE REGISTER. The VBR contains the base address of the exception vector table in memory. The displacement of an exception vector is added to the value in this register to access the vector table. Refer to Section 8 Exception Processing for infor- mation on exception vectors. M68060 USER’S MANUAL MOTOROLA...

-

Page 69: Processor Configuration Register

This bit is cleared at reset. Bits 6–2—Reserved by Motorola for future use and must always be zero. DFP—Disable Floating-Point Unit When this bit is set, the on-chip FPU is disabled and any attempt to execute a floating- point instruction generates a line F emulator exception. - Page 70 ATC. ATC accesses operate in parallel with indexing into the on-chip instruction and data caches. The MMU MDIS signal dynami- cally disables address translation for emulation and diagnostic support. MOTOROLA M68060 USER’S MANUAL...

-

Page 71: Memory Management Unit

When the translation is obtained, it is used for the cache lookup, and is placed in the ATC for future use. The table search is performed automatically by the MC68060 using on-chip logic. M68060 USER’S MANUAL MOTOROLA... -

Page 72: Memory Management Programming Model

32-bit URP and SRP registers. Bits 8–0 of an address loaded into the URP or the SRP must be zero. Transfers of data to and from these 32-bit registers are long-word trans- fers. USER ROOT POINTER SUPERVISOR ROOT POINTER Figure 4-3. URP and SRP Register Formats MOTOROLA M68060 USER’S MANUAL... -

Page 73: Translation Control Register Format

0 0 0 0 0 0 0 0 0 0 0 0 0 0 FOTC FITC Figure 4-4. Translation Control Register Format Bits 31–16—Reserved by Motorola. Always read as zero. E—Enable This bit enables and disables paged address translation. 0 = Disable 1 = Enable A reset operation clears this bit. - Page 74 11 = Cache-inhibited, imprecise exception model DUI—Default UPA Bits (Instruction Cache) These bits are two user-defined bits for instruction prefetch bus cycles (see 4.2.2.3 Descriptor Field Definitions ) Bit 0—Reserved by Motorola. Always read as zero. MOTOROLA M68060 USER’S MANUAL...

-

Page 75: Transparent Translation Register Format

1 X = Ignore FC2 when matching U0, U1—User Page Attributes The user defines these bits, and the MC68060 does not interpret them. U0 and U1 are echoed to the UPA0 and UPA1 signals, respectively, if an external bus transfer results M68060 USER’S MANUAL MOTOROLA... - Page 76 This bit indicates the write privilege of the TTR block. 0 = Read and write accesses permitted 1 = Write accesses not permitted Bits 4,3,1,0—Reserved by Motorola. 4.2 LOGICAL ADDRESS TRANSLATION The primary function of the MMUs is to translate logical addresses to physical addresses.

-

Page 77: Translation Table Structure

23 bits to produce the phys- ical address of the pointer-level table descriptor. Each of the 128 pointer-level table descrip- tors corresponds to a 256-Kbyte block of memory. M68060 USER’S MANUAL MOTOROLA... - Page 78 This is a functional difference between the MC68060 and the MC68040. Table and page descriptors must not be left in a state that is incoherent to the processor. Violation of this restriction can result in an undefined operation. Page descriptors must not MOTOROLA M68060 USER’S MANUAL...

-

Page 79: Detailed Flowchart Of Table Search Operation

FC2, LA, DF[G] ATC ENTRY PFA, DF[U1,U0,S,CM,M],WP ABBREVIATIONS: PFA - PAGE FRAME ADDRESS EXIT TABLE SEARCH DF[ ] - DESCRIPTOR FIELD WP - ACCUMULATED WRITE- PROTECTION STATUS ASSIGNMENT OPERATOR Figure 4-8. Detailed Flowchart of Table Search Operation 4-10 M68060 USER’S MANUAL MOTOROLA... -

Page 80: Detailed Flowchart Of Descriptor Fetch Operation

THE NEXT LEVEL DESCRIPTOR. NORMAL TERMINATION ABBREVIATIONS: OF ALL BUS TRANSFERS WP – ACCUMULATED WRITE- PROTECTION STATUS V – LOGICAL "OR" OPERATOR RETURN EXIT TABLE SEARCH – ASSIGNMENT OPERATOR Figure 4-9. Detailed Flowchart of Descriptor Fetch Operation MOTOROLA M68060 USER’S MANUAL 4-11... -

Page 81: Page Descriptor Formats

UR G U1 U0 4K PAGE DESCRIPTOR (PAGE LEVEL) 13 12 11 10 PHYSICAL ADDRESS UR UR G U1 U0 8K PAGE DESCRIPTOR (PAGE LEVEL) DESCRIPTOR ADDRESS INDIRECT PAGE DESCRIPTOR (PAGE LEVEL) Figure 4-11. Page Descriptor Formats 4-12 M68060 USER’S MANUAL MOTOROLA... - Page 82 This code indicates that the descriptor is an indirect descriptor. Bits 31–2 contain the physical address of the page descriptor. This encoding is invalid for a page descriptor pointed to by an indirect descriptor (that is, only one level of indirection is allowed). MOTOROLA M68060 USER’S MANUAL 4-13...

- Page 83 Setting the W-bit in a table descriptor write protects all pages accessed with that descrip- tor. When the W-bit is set, a write access or a locked read-modify-write access to the log- ical address corresponding to this entry causes an access error exception to be taken. 4-14 M68060 USER’S MANUAL MOTOROLA...

-

Page 84: Example Translation Table

Memory Management Unit X—Motorola Reserved These bit fields are reserved for future use by Motorola. 4.2.3 Translation Table Example Figure 4-12 illustrates an access example to the logical address $76543210 while in the supervisor mode with an 8-Kbyte memory page size. The RI field of the logical address, $3B, is mapped into bits 8–2 of the SRP value to select a 32-bit root table descriptor at a root-... -

Page 85: Translation Table Using Indirect Descriptors

TABLE $00 TABLE $15 TABLE $3B ROOT POINTER TASK A $00001800 $00003000 $80000010 TABLE $7F TABLE $1F ROOT POINTER TASK B FRAME ADDRESS ROOT-LEVEL POINTER-LEVEL PAGE-LEVEL TABLES TABLES TABLES Figure 4-13. Translation Table Using Indirect Descriptors 4-16 M68060 USER’S MANUAL MOTOROLA... - Page 86 This access may be to a previously unused area or for data that is no longer resident in memory. If the access error handler adds to and updates the translation MOTOROLA M68060 USER’S MANUAL 4-17...

- Page 87 This technique allows the operating system to construct a minimal translation table for each task, conserving physical memory utilization and minimizing operating system overhead. 4-18 M68060 USER’S MANUAL MOTOROLA...

- Page 88 (W = 0) and the access is not a supervisor violation (for user accesses, the S-bit of the page descriptor must be clear), then the M-bit is set using a simple write. The U- and M-bits are MOTOROLA M68060 USER’S MANUAL 4-19...

-

Page 89: Updating U-Bit And M-Bit For

The MC68060 MMUs provide separate translation tables for supervisor and user address spaces. The translation tables contain both mapping and protection information. Each table and page descriptor includes a write-protect (W) bit that can be set to provide write protec- 4-20 M68060 USER’S MANUAL MOTOROLA... -

Page 90: Translation Table Structure For Two Tasks

URP FOR TASK 'B' • TRANSLATION • TABLE FOR TASK 'B' • POINTER SUPERVISOR A LEVEL TABLE COMMON SRP TRANSLATION • TABLE FOR • ALL SUPERVISOR • ACCESSES Figure 4-16. Translation Table Structure for Two Tasks MOTOROLA M68060 USER’S MANUAL 4-21... -

Page 91: Logical Address Map With Shared Supervisor And User Address Spaces

THIS AREA IS SUPERVISOR ONLY, READ-ONLY THIS AREA IS SUPERVISOR ONLY, READ/WRITE THIS AREA IS SUPERVISOR OR USER, READ-ONLY THIS AREA IS SUPERVISOR OR USER, READ/WRITE Figure 4-17. Logical Address Map with Shared Supervisor and User Address Spaces 4-22 M68060 USER’S MANUAL MOTOROLA... -

Page 92: Translation Table Using S-Bit And W-Bit To Set Protection

W = 0 THIS PAGE SUPERVISOR/USER, READ/WRITE W = 0 S = 0,W = 0 ROOT-LEVEL POINTER-LEVEL PAGE-LEVEL TABLE TABLE TABLE NOTE: X = DON'T CARE Figure 4-18. Translation Table Using S-Bit and W-Bit To Set Protection MOTOROLA M68060 USER’S MANUAL 4-23... -

Page 93: Atc Organization

Each ATC entry consists of a physical address, attribute information from a corresponding page descriptor, and a tag that contains a logical address and status information. Figure 4- 20, which illustrates the entry and tag fields, is followed by field definitions listed in alphabet- ical order. 4-24 M68060 USER’S MANUAL MOTOROLA... -

Page 94: Atc Entry And Tag Fields

ATC with the M-bit clear. Physical Address The upper bits of the translated physical address are contained in this field. MOTOROLA M68060 USER’S MANUAL 4-25... - Page 95 The MMU is organized such that other operations always completely overlap the translation time of the ATCs; thus, no performance penalty is associated with ATC searches. The address translation occurs in parallel with indexing into the on-chip instruction and data caches. 4-26 M68060 USER’S MANUAL MOTOROLA...

- Page 96 If both registers match, the TT0 status bits are used for the access. Transparent translation can also be implemented by the translation tables of the translation tables if the physical addresses of pages are set equal to their logical addresses. MOTOROLA M68060 USER’S MANUAL 4-27...

- Page 97 A reset of the processor does not invalidate any entries in the ATCs page size. A PFLUSH instruction must be executed to flush all existing valid entries from the ATCs after a reset 4-28 M68060 USER’S MANUAL MOTOROLA...

-

Page 98: Address Translation Flowchart

ATC ENTRY [CM] EXIT * Refers to either instruction or data transparent translation register. Figure 4-21. Address Translation Flowchart operation and before translation is enabled. PFLUSH can be executed even if the E-bit is cleared. MOTOROLA M68060 USER’S MANUAL 4-29... - Page 99 There are two variants of PLPA, which are PLPAR and PLPAW, which check the privilege and set the table and ATC history bits as if a read or write access, respectively, were being performed. 4-30 M68060 USER’S MANUAL MOTOROLA...

- Page 100 (128 bits) of data. The status information for the instruction cache is a single valid bit for the line. The status information for the data cache is a valid bit and a dirty MOTOROLA M68060 USER’S MANUAL...

-

Page 101: Mc68060 Instruction And Data Caches

A cache line is always in one of three states: invalid, valid, or dirty. For invalid lines, the V- bit is clear, causing the cache line to be ignored during lookups. Valid lines have their V-bit set and D-bit cleared, the line contains valid data consistent with memory. Dirty cache lines M68060 USER’S MANUAL MOTOROLA... -

Page 102: Caching Operation

10–4 are used to index into the cache and select 1 of 128 sets of cache lines. Physical address bits 31–11 are used as a tag reference or to update the cache line tag MOTOROLA M68060 USER’S MANUAL... - Page 103 (MMU) page descriptor or transparent translation register) bypass the cache to al- low support for I/O, etc. Valid data cache entries that match during non-cachable address accesses are pushed and invalidated if dirty and are invalidated if not dirty. M68060 USER’S MANUAL MOTOROLA...

- Page 104 0 = Each cache line is invalidated as it is pushed. Affects only the data cache. 1 = CPUSHed lines remain valid in the cache. FOC—1/2 Cache Operation Mode Enable (Data Cache) 0 = The data cache operates in normal, full-cache mode. 1 = The data cache operates in 1/2-cache mode. MOTOROLA M68060 USER’S MANUAL...

- Page 105 CACR. The caches are disabled immediately after the current access completes. If CDIS is asserted during the access for the first half of a misaligned operand spanning two cache lines, the M68060 USER’S MANUAL MOTOROLA...

- Page 106 Otherwise, the data is read from memory and used to update the cache. Since instruction cache accesses are always reads, the selection of writethrough or copyback modes do not affect them. The following paragraphs describe the writethrough and copyback modes in detail. MOTOROLA M68060 USER’S MANUAL...

- Page 107 (i.e. that must be read from the bus). Precise operation forces operand read accesses for an instruction to occur only once by preventing the instruc- tion from being interrupted after the operand fetch stage. Otherwise, if not in precise mode M68060 USER’S MANUAL MOTOROLA...

- Page 108 Write misses to writethrough pages write directly to memory without loading the corresponding cache line in the cache. Snooped external writes that miss in the cache have no affect on the cache. MOTOROLA M68060 USER’S MANUAL...

- Page 109 (i.e., resulting from self-modifying code or from code executed to load a new page from disk) access memory through the data memory unit. Because the instruction cache does not monitor these data accesses, stale data occurs in the instruction 5-10 M68060 USER’S MANUAL MOTOROLA...

-

Page 110: Tlnx Encoding

(as defined by TA) for a total of MOTOROLA M68060 USER’S MANUAL 5-11... - Page 111 (e.g., the second half of a misaligned operand), the processor immediately takes an exception. Otherwise, no exception occurs, and the cache line fill is repeated the next time data within the line is 5-12 M68060 USER’S MANUAL MOTOROLA...

- Page 112 Once the bus transaction (burst read) completes, the MC68060 is able to generate the appropriate line write bus transaction to store the contents of the push buffer into memory. MOTOROLA M68060 USER’S MANUAL 5-13...

- Page 113 The branch cache plays a major role in achieving the performance levels of the MC68060 processor. The branch cache provides a table associating branch program counter values with the corresponding branch target virtual addresses. The fundamental concept is to pro- 5-14 M68060 USER’S MANUAL MOTOROLA...

- Page 114 If available, an invalid line is selected and updated with the tag and data from memory. The line state then changes from invalid to valid by setting the V-bit. If all lines in the set are already valid, a pseudo round-robin replacement algorithm is used to select one MOTOROLA M68060 USER’S MANUAL 5-15...

- Page 115 Figure 5-6 illustrates the instruction-cache line state transitions resulting from pro- cessor and snoop controller accesses. Transitions are labeled with a capital letter, indicating the previous state, followed by a number indicating the specific case listed in Table 5-2. 5-16 M68060 USER’S MANUAL MOTOROLA...

-

Page 116: Instruction Cache Line State Diagram

The data cache supports a line-based protocol allowing individual cache lines to be in one of three states: invalid, valid, or dirty. To maintain coherency with memory, the data cache supports both writethrough and copyback modes, specified by the CM field for the page. MOTOROLA M68060 USER’S MANUAL 5-17... -

Page 117: Data Cache Line State Diagrams

WI3—CPU WRITE MISS WV3—CPU WRITE MISS WI5—CINV WV4—CPU WRITE HIT WI6—CPUSH WI1— CPU READ MISS WRITE- WRITE- THROUGH THROUGH VALID INVALID WV5— CINV WV6— CPUSH WV7—SNOOP HIT WRITETHROUGH CACHING MODE Figure 5-7. Data Cache Line State Diagrams 5-18 M68060 USER’S MANUAL MOTOROLA... -

Page 118: Data Cache Line State Transitions

DPI bit the the CACR. Alternate (C,W)V7 No action; Go to invalid CD7 No action (dirty data lost); Master (C,W)I7 Not possible. state. Go to invalid state. Snoop Hit 5-19 M68060 USER’S MANUAL MOTOROLA... - Page 119 The MC68060 FPU operates in parallel with the integer unit. The FPU does the numeric calculation while the integer unit performs other tasks. When used with Motorola-supplied emulation software, the M68060 software pack- age (M68060SP), the MC68060 FPU is fully compliant with the ANSI/IEEE 754–1985 Stan- dard for Binary Floating-Point Arithmetic .

-

Page 120: Floating-Point Unit Block Diagram

The MC68060 fully conforms to the ANSI/IEEE 754–1985 Standard for Binary Float- ing-Point Arithmetic . In addition, the MC68060 processor maintains compatibility with the Motorola extended-precision architecture and is user object code compatible with the MC68881/MC68882 floating-point coprocessors and the MC68040 microprocessor FPU. -

Page 121: Floating-Point User Programming Model

(MODE) byte that sets the user-selectable modes. The user can read or write to the FPCR. Motorola reserves bits 31–16 for future definition; these bits are always read as zero and are ignored during write operations. -

Page 122: Floating-Point Control Register Format

The reset function or a restore operation of the null state clears the FPSR. Floating-point conditional operations are not guaranteed if the FPSR is written directly, because the FPSR is only valid as a result of a floating-point instruction. M68060 USER’S MANUAL MOTOROLA... -

Page 123: Floating-Point Condition Code (Fpsr)

The start of most operations clears this byte; however, operations that cannot generate floating-point exceptions (the FMOVEM and FMOVE control register instructions) do not clear this byte. An exception handler can use this byte to determine which floating- point exception(s) caused a trap. MOTOROLA M68060 USER’S MANUAL... -

Page 124: Floating-Point Exception Status Byte (Fpsr)

AEXC bit with a combination of bits in the EXC byte derives a new value in the corresponding AEXC bit. These equations apply to setting the AEXC bits at the end of each operation affecting the AEXC byte: M68060 USER’S MANUAL MOTOROLA... -

Page 125: Mc68060 Fpu Data Formats And Data Types

— † — — — Denormalized † † † † — — — Unnormalized — — † † — — — Data Format/Type Supported by On-Chip MC68060 FPU Hardware † Data Format/Type Supported by Software (M68060SP) MOTOROLA M68060 USER’S MANUAL... -

Page 126: Single-Precision Real Format Summary

Nonzero Bit Pattern Created by User xxxxx…xxxx Fraction When Created by FPU 11111…1111 Approximate Ranges 3.4 × 10 38 Maximum Positive Normalized 1.2 × 10 –38 Minimum Positive Normalized 1.4 × 10 –45 Minimum Positive Denormalized M68060 USER’S MANUAL MOTOROLA... -

Page 127: Double-Precision Real Format Summary

Nonzero Bit Pattern Created by User .xxxxx…xxxx Fraction When Created by FPU .11111…1111 Approximate Ranges 1.8 x 10 308 Maximum Positive Normalized 2.2 x 10 –308 Minimum Positive Normalized 4.9 x 10 –324 Minimum Positive Denormalized MOTOROLA M68060 USER’S MANUAL... -

Page 128: Extended-Precision Real Format Summary

Don’t Care Explicit Integer Bit Don’t Care Biased Exponent Format Maximum 32767 ($7FFF) Mantissa Nonzero Representation of Mantissa Nonsignaling x.1xxxx…xxxx Signaling x.0xxxx…xxxx Nonzero Bit Pattern Created by User x.xxxxx…xxxx Mantissa When Created by FPU 1.11111…1111 6-10 M68060 USER’S MANUAL MOTOROLA... -

Page 129: Packed Decimal Real Format Summary

IEEE 754 standard, but does not sup- port extended precision. The results are the same when performing the same operation in extended precision and storing the results in single- or double-precision format. MOTOROLA M68060 USER’S MANUAL 6-11... -

Page 130: Intermediate Result Format

If the destination is a memory location, the FPCR PREC bits are ignored. In this case, a number in the extended-precision format is taken from the source floating- point data register, rounded to the destination format precision, and then written to memory. 6-12 M68060 USER’S MANUAL MOTOROLA... - Page 131 67-bit mantissa allows the FPU to meet the error bound of the IEEE specification: The least significant bit of the rounded result does not increment even though the guard bit is set in the intermediate result. The IEEE 754 standard specifies that tie cases should be MOTOROLA M68060 USER’S MANUAL 6-13...

-

Page 132: Rounding Algorithm Flowchart

2 (the value of the guard bit). This error is equal to one-half of the least significant bit’s value and is the worst case error that can be introduced when using the RN 6-14 M68060 USER’S MANUAL MOTOROLA... - Page 133 If a number has grossly underflowed, the MC68060 takes a non- maskable underflow exception, and the M68060SP returns a zero or the smallest denormal- ized number with the correct sign, depending on the rounding mode in effect. MOTOROLA M68060 USER’S MANUAL 6-15...

-

Page 134: Floating-Point Condition Code Encoding

MC68060 logically combines the four FPCC bits to form 32 conditional tests. The 32 conditional tests are separated into two groups—16 6-16 M68060 USER’S MANUAL MOTOROLA... - Page 135 BSUN bit is set in the FPSR EXC byte for the 32 floating-point conditional tests. The equation column lists the combination of FPCC bits for each test in the form of an equa- tion. MOTOROLA M68060 USER’S MANUAL 6-17...

-

Page 136: Floating-Point Conditional Tests

False 000000 True True 001111 Signaling False False 010000 Signaling True True 011111 Signaling Equal 010001 Signaling Not Equal 011110 NOTE: All condition codes with an overbar indicate cleared bits; all other bits are set. 6-18 M68060 USER’S MANUAL MOTOROLA... -

Page 137: Floating-Point Exception Vectors

Table 6-11 lists the floating-point instructions which are unimplemented on the MC68060. Refer to 8.2.4 Illegal Instruction and Unimplemented Instruction Exceptions for back- ground material. Motorola provides the M68060SP, a software package that includes float- ing-point emulation for the MC68060. Refer to Appendix C for software porting information. -

Page 138: Unimplemented Instructions

11 for the unimplemented F-line instruction exception vector, fetches the address of the F-line exception handler from the processor’s exception vector table, pushes the format $2 stack frame on the system stack, and begins execution of the exception handler after prefetching instructions to fill the pipeline. 6-20 M68060 USER’S MANUAL MOTOROLA... - Page 139 (if any). The M68060SP provides the routines needed to com- plete the instruction and stores the result to the proper destination, whether it be in a floating- point data register, integer data register, or external memory. Once the destination is written, MOTOROLA M68060 USER’S MANUAL 6-21...

- Page 140 This section discusses the operation of the MC68060, with the aid of the M68060SP, and how information is perceived and used by the user-supplied exception handler. It is assumed in this section that the M68060SP is already ported properly to the MC68060 sys- tem. 6-22 M68060 USER’S MANUAL MOTOROLA...

- Page 141 As outlined in 6.5.1 Unimplemented Floating-Point Instructions to 6.5.3 Unimple- mented Effective Address Exception, there are certain conditions such that the M68060SP reports floating-point arithmetic exceptions as part of handling an unimple- mented floating-point instruction, unimplemented effective address, or unsupported data MOTOROLA M68060 USER’S MANUAL 6-23...

- Page 142 A $0 stack frame is saved, and vector number 48 is gen- erated to access the BSUN exception vector. The BSUN entry in the processor’s vector table points to the user BSUN exception handler. 6-24 M68060 USER’S MANUAL MOTOROLA...

- Page 143 NAN are modified, although the input NAN is truncated if necessary. If the destination data format is B, W, or L, then the 8, 16, or 32 most significant bits of the SNAN significand, with the SNAN bit set, are written to the destination. MOTOROLA M68060 USER’S MANUAL 6-25...

- Page 144 Table 6-12 lists the possible operand errors, both native and non-native to the MC68060, which the M68060SP unimplemented instruction exception handler can report. When an operand error occurs, the OPERR bit is set in the FPSR EXC byte. 6-26 M68060 USER’S MANUAL MOTOROLA...

-

Page 145: Possible Operand Errors Exceptions

NAN is stored in the destination. 6.6.3.2 TRAP ENABLED RESULTS (FPCR OPERR BIT SET). For FMOVE cases, the destination is written as if the trap were disabled, and then control is passed to MOTOROLA M68060 USER’S MANUAL 6-27... - Page 146 OVFL handler (the OVFL bit in the FPCR exception enable byte is set), or to the user INEX handler (the OVFL bit in the FPCR exception enable byte is cleared, but the INEX bit in the 6-28 M68060 USER’S MANUAL MOTOROLA...

-

Page 147: Overflow Rounding Mode Values

15-bit format. In addition to normal overflow, the exponential instructions (e , 10 , SINH, COSH, and FSCALE) may generate results that grossly overflow the 16-bit exponent of the internal MOTOROLA M68060 USER’S MANUAL 6-29... - Page 148 IEEE exception enabled definition since it is set any time a tiny number is generated. The MC68060 is implemented such that when the UNFL bit of the FPCR is set, the proces- sor always takes an exception regardless of whether or not the user UNFL exception han- 6-30 M68060 USER’S MANUAL MOTOROLA...

-

Page 149: Underflow Rounding Mode Values

UNFL handler as a post-instruction exception. Otherwise, if the destination is a floating-point data register, control is passed to the user UNFL handler as a pre-instruction exception when the next floating-point instruction is encountered. MOTOROLA M68060 USER’S MANUAL 6-31... - Page 150 When a divide-by-zero is detected, the DZ bit is set in the FPSR EXC byte. The divide- by-zero exception only has maskable exceptional conditions. An exception is taken only if the DZ bit is set in FPSR EXC byte and the corresponding bit in the FPCR exception enable byte is set. 6-32 M68060 USER’S MANUAL MOTOROLA...

-

Page 151: Possible Divide-By-Zero Exceptions

If either of the two inex- act exceptions is enabled, the processor fetches the inexact exception vector, and the user INEX exception handler is initiated. INEX refers to both exceptions in the following para- graphs. MOTOROLA M68060 USER’S MANUAL 6-33... -

Page 152: Rounding Mode Values

If the instruction is an FMOVE OUT, the integer stack frame format $3 contains the effective address of the destination memory operand. If the destination is an integer data register, the effective address field is undefined. 6-34 M68060 USER’S MANUAL MOTOROLA... -

Page 153: Floating-Point State Frame

Figure 6-10. Floating-Point State Frame Bits 15–8 of the first long word of the floating-point frame define the frame format. The legal formats for the MC68060 are: Null Frame (NULL) Idle Frame (IDLE) Exception Frame (EXCP) MOTOROLA M68060 USER’S MANUAL 6-35... -

Page 154: Status Word Contents

The FRESTORE of an EXCP state is used in the M68060SP to provide to the user exception handler the illusion that the M68060SP handler never existed at all. The user exception handler is entered with the FPU in the proper exception state. The user 6-36 M68060 USER’S MANUAL MOTOROLA... - Page 155 $3FFF+$6000 instead of $3FFF. If catastrophic underflow, $0. INEX—Undefined if INEX only. Otherwise if either SNAN, OPERR, UNFL, or OVFL also set in FPSR, use exception operand defined for either SNAN, OPERR, UNFL, or OVFL. MOTOROLA M68060 USER’S MANUAL 6-37...

- Page 156 CLK before they are three-stated. Refer to Figure 7-2, Fig- ure 7-3, and Figure 7-4 for an illustration. Furthermore, the processor status signals (PSTx), RSTO, and IPEND output signals are updated on rising edges of CLK regardless of the CLKEN input. MOTOROLA M68060 USER’S MANUAL...

-

Page 157: Signal Relationships To Clocks

= Required input hold time relative to CLK rising edge. Figure 7-1. Signal Relationships to Clocks CLKEN BCLK BB or TIP THREE-STATING FROM ASSERTED STATE Figure 7-2. Full-Speed Clock CLKEN BCLK BB or TIP THREE-STATING FROM ASSERTED STATE Figure 7-3. Half-Speed Clock M68060 USER’S MANUAL MOTOROLA... -

Page 158: Quarter-Speed Clock

CLK, CLKEN, and BCLK for quarter-speed bus operation. Note that once BCLK has been established, inputs and outputs appear to be synchronized to this virtual BCLK. To simplify the description of MC68060 bus operation, the rising edges MOTOROLA M68060 USER’S MANUAL... -

Page 159: Bus Control Register Format

Figure 7-5. Bus Control Register Format L—Lock Bit 0 = Negate external LOCK signal. 1 = Assert external LOCK signal. SL—Shadow Copy, Lock Bit 0 = LOCK negated sequence at time of exception. 1 = LOCK asserted at time of exception. M68060 USER’S MANUAL MOTOROLA... -

Page 160: Internal Operand Representation

Unlike the MC68020 and MC68030 processors, the MC68060 does not support dynamic bus sizing and expects the referenced device to accept the requested access width. The MC68150 dynamic bus sizer is designed to allow the 32-bit MC68060 bus to communicate MOTOROLA M68060 USER’S MANUAL... -

Page 161: Data Multiplexing

A1 and A0 indicate the byte offset from the base. For long-word or line bus cycles, external logic must ignore address bits A1 and A0 for proper operation. M68060 USER’S MANUAL MOTOROLA... -

Page 162: Data Bus Requirements For Read And Write Cycles

A brief summary of the bus signal encoding for each access type is listed in Table 7-2. Addi- tional information on the encoding for the MC68060 signals can be found in Section 2 Sig- nal Description . MOTOROLA M68060 USER’S MANUAL... -

Page 163: Byte Select Signal Generation And Pal Equation

; word aligned, word or line size + SIZ1 * SIZ0 ; enable every byte for long-word size + /SIZ1 * /SIZ0 ; enable every byte for line size Figure 7-8. Byte Select Signal Generation and PAL Equation M68060 USER’S MANUAL MOTOROLA... -

Page 164: Summary Of Access Types Vs. Bus Signal Encoding

Misaligned operand accesses that miss in the data cache are cachable and are not aligned before line filling. Refer to Section 5 Caches for details on line fill and the data cache. MOTOROLA M68060 USER’S MANUAL... -

Page 165: Example Of A Misaligned Long-Word Transfer

Register 24 23 16 15 — — DATA BUS 24 23 16 15 — — — TRANSFER 1 — — — TRANSFER 2 MEMORY 24 23 16 15 Figure 7-10. Example of Misaligned Word Transfer 7-10 M68060 USER’S MANUAL MOTOROLA... -

Page 166: Misaligned Long-Word Read Bus Cycle Timing

The table confirms that alignment significantly affects bus cycle throughput for non- cachable accesses. For example, in Figure 7-9 the misaligned long-word operand took three bus cycles because the byte offset = $1. If the byte offset = $0, then it would have taken one MOTOROLA M68060 USER’S MANUAL 7-11... -

Page 167: Memory Alignment Influence On Noncachable And Writethrough Bus Cycles

• Accesses to a disabled cache • Accesses to a memory page that is specified noncachable • Accesses that are implicitly noncachable (locked read-modify-write accesses, access- es to an alternate logical address space via the MOVES instruction, and table searches) 7-12 M68060 USER’S MANUAL MOTOROLA... -

Page 168: Byte, Word, And Long-Word Read Cycle Flowchart

Cache inhibit out (CIOUT) is asserted since the ac- cess is identified as noncachable. Refer to Section 4 Memory Management Unit for in- formation on the MC68060 and MC68LC060 memory units and Appendix B MC68EC060 for information on the MC68EC060 memory unit. MOTOROLA M68060 USER’S MANUAL 7-13... -

Page 169: Byte, Word, And Long-Word Read Bus Cycle Timing

The processor asserts transfer start (TS) during C1 to indicate the beginning of a bus cy- cle. If not already asserted from a previous bus cycle, the transfer in progress (TIP) signal is also asserted at this time to indicate that a bus cycle is active. 7-14 M68060 USER’S MANUAL MOTOROLA... - Page 170 The processor responds by terminating the line burst transfer and accessing the remainder of the line, using three long-word read bus cycles. Although the selected device can then treat the line bus cycle as four, independent, long-word bus MOTOROLA M68060 USER’S MANUAL 7-15...

- Page 171 The MC68060 implements a special mode called the acknowledge termination ignore state capability to aid in high-frequency designs. In this mode, the processor begins sam- pling termination signals such as TA after a user-programmed number of BCLK rising 7-16 M68060 USER’S MANUAL MOTOROLA...

-

Page 172: Line Read Cycle Flowchart

Figure 7-14. Line Read Cycle Flowchart edges has expired. The signal SAS is provided as a status output to indicate which BCLK rising edge the processor begins to sample the termination signals. If this mode is dis- MOTOROLA M68060 USER’S MANUAL 7-17... -

Page 173: Line Read Transfer Timing

If TA is not recognized asserted, the processor ignores the data and inserts wait states instead of terminating the transfer. The processor continues to sample TA, TBI, and TCI on successive rising edges of BCLK until TA is recognized 7-18 M68060 USER’S MANUAL MOTOROLA... - Page 174 Otherwise, the processor negates TIP during the next clock. Figure 7-16 and Figure 7-17 illustrate a flowchart and functional timing diagram for a burst-inhibited line read bus cycle. MOTOROLA M68060 USER’S MANUAL 7-19...

-

Page 175: Burst-Inhibited Line Read Cycle Flowchart

• Cache line pushes for lines containing a single dirty long word. Figure 7-18 and Figure 7-19 illustrate a flowchart and functional timing diagram for byte, word, and long-word write bus transfers. 7-20 M68060 USER’S MANUAL MOTOROLA... -

Page 176: Burst-Inhibited Line Read Bus Cycle Timing

LONG BS3–BS0 CIOUT A3–A2 D31–D0 INHIBITED LONG-WORD LONG-WORD LONG-WORD LINE READ READ READ READ NOTE: It is assumed that the acknowledge termination ignore state capability is disabled. Figure 7-17. Burst-Inhibited Line Read Bus Cycle Timing MOTOROLA M68060 USER’S MANUAL 7-21... -

Page 177: Byte, Word, And Long-Word Write Transfer Flowchart

LANES BASED ON SIZ1–SIZ0, A1–A0, OR BS3–BS0 3) ASSERT TA FOR ONE BCLK 1) THREE-STATE DATA BUS 2) NEGATE LOCK, LOCKE IF NECESSARY 1) NEGATE TIP OR START NEXT CYCLE Figure 7-18. Byte, Word, and Long-Word Write Transfer Flowchart 7-22 M68060 USER’S MANUAL MOTOROLA... -

Page 178: Long-Word Write Bus Cycle Timing

BYTE WORD LONG D31–D0 DRIVE DRIVE DRIVE WORD WRITE LONG-WORD BYTE WRITE WITH WAIT WRITE NOTE: It is assumed that the acknowledge termination ignore state capability is disabled. Figure 7-19. Long-Word Write Bus Cycle Timing MOTOROLA M68060 USER’S MANUAL 7-23... - Page 179 The data bus then three-states and the bus cycle ends. When the processor recognizes TA at the rising BCLK edge and terminates the bus cycle, TIP remains asserted if the processor is ready to begin another bus cycle. Otherwise, the 7-24 M68060 USER’S MANUAL MOTOROLA...

- Page 180 If TA is not recognized asserted, the processor inserts wait states instead of terminating the transfer. The processor continues to sample TA and TBI on successive rising edges of BCLK until TA is recognized asserted. If TBI was negated with the asser- MOTOROLA M68060 USER’S MANUAL 7-25...

-

Page 181: Line Write Cycle Flowchart

In this case, the processor increments A3 and A2 for each write, and the new address is placed on the address bus for each bus cycle. Refer to 7.7.3 Byte, Word, and Long-Word Write Cycles for information on long-word writes. If no wait 7-26 M68060 USER’S MANUAL MOTOROLA... -

Page 182: Line Write Burst-Inhibited Cycle Flowchart

Clock 5 (C5) This clock is identical to C3 except that the value driven on the data bus corresponds to the fourth long word of data for the burst. After the processor recognizes the last TA as- MOTOROLA M68060 USER’S MANUAL 7-27... -

Page 183: Line Write Bus Cycle Timing

The locked read-modify-write sequence performs a read, conditionally modifies the data in the processor, and writes the data out to memory. In the MC68060, this operation can be indivisible, providing semaphore capabilities for multiprocessor systems. During the entire 7-28 M68060 USER’S MANUAL MOTOROLA... - Page 184 TA and registers the current value on the data bus. If TA is asserted, the read transfer terminates and the registered data is passed to the appropriate memory unit. If TA is not MOTOROLA M68060 USER’S MANUAL 7-29...

-

Page 185: Locked Bus Cycle For Tas Instruction Timing

BCLK until TA is recognized as asserted. The registered data is then passed to the appropriate memory unit. If more than one read cycle is required to read in the operand(s), C1 and C2 are repeated accordingly. 7-30 M68060 USER’S MANUAL MOTOROLA... - Page 186 The CAS2 and CAS (with misaligned operands) are not supported in hardware by the MC68060. If these instructions are encountered, an unimplemented integer exception is taken. Once the opcode for a CAS2 or CAS is decoded, the MOVEC instruction to the MOTOROLA M68060 USER’S MANUAL 7-31...

- Page 187 IPLx must maintain the interrupt request level until the MC68060 acknowledges the interrupt to guarantee that the interrupt is recognized. The MC68060 continuously samples IPLx on consecutive rising edges of CLK to synchronize 7-32 M68060 USER’S MANUAL MOTOROLA...

-

Page 188: Using Cla In A High-Speed Dram Design

The MC68060 asserts IPEND when an interrupt request is pending. Figure 7-26 illustrates the assertion of IPEND relative to the assertion of an interrupt level on the IPLx signals. IPEND signals external devices that an interrupt exception will be taken at an upcoming MOTOROLA M68060 USER’S MANUAL 7-33... -

Page 189: Assertion Of Ipend

High High rupt Exception Either High High Take Autovectored Interrupt Exception MC68040 High Don’t Care Retry Interrupt Acknowledge Cycle Native-MC68060 Don’t Care High Don’t Care MC68040 Don’t Care Don’t Care Don’t Care Illegal Combination, Unsupported 7-34 M68060 USER’S MANUAL MOTOROLA... - Page 190 (TEA). In this case, the MC68060 automatically generates the spurious interrupt vector number 24 ($18) instead of the interrupt vector number. If operating in the MC68040 acknowledge termination mode, MOTOROLA M68060 USER’S MANUAL 7-35...

-

Page 191: Interrupt Acknowledge Cycle Flowchart

TA or TEA, the processor takes an illegal instruction exception. A retry termination simply retries the breakpoint acknowledge cycle. Figure 7-30 and Figure 7-31 illustrate a flowchart and functional timing diagram for a breakpoint acknowledge bus cycle. 7-36 M68060 USER’S MANUAL MOTOROLA... -

Page 192: Interrupt Acknowledge Bus Cycle Timing

Figure 7-28. Interrupt Acknowledge Bus Cycle Timing Note that the acknowledge termination ignore state capability is applicable to the breakpoint acknowledge cycle. If enabled, TA, TEA, and TRA are ignored for a user-programmed num- ber of BCLK cycles. MOTOROLA M68060 USER’S MANUAL 7-37... -

Page 193: Autovector Interrupt Acknowledge Bus Cycle Timing

LPSTOP broadcast cycle. This access is a write bus cycle and is indicated with TT1, TT0 = $3, A31–A0 = $FFFFFFFE, and TM2–TM0 = $0. When an external device ter- minates the cycle with either TA or TEA, the processor enters the low-power stop mode. A 7-38 M68060 USER’S MANUAL MOTOROLA... -

Page 194: Breakpoint Interrupt Acknowledge Cycle Flowchart

CLK only be stopped when the PSTx signals indicate $16. Figure 7-32 illustrates a flowchart of the LPSTOP broadcast cycle. Figure 7-33 and Figure 7-34 illustrate functional timing diagrams for an LPSTOP broadcast cycle as a function of MOTOROLA M68060 USER’S MANUAL 7-39... -

Page 195: Breakpoint Interrupt Acknowledge Bus Cycle Timing

BB, TRA, TA, TEA, CLA, BGR, BG, SNOOP, AVEC, MDIS, CDIS, TCI, and TBI. The processor uses the PSTx encoding of $18 to indicate exception processing. 7-40 M68060 USER’S MANUAL MOTOROLA... -

Page 196: Lpstop Broadcast Cycle Flowchart

BGR and AVEC signals is not necessary because these signals are significant only during locked sequences (BGR) and interrupt acknowledge cycles (AVEC), neither of which is pending when exiting the LPSTOP condition. MOTOROLA M68060 USER’S MANUAL 7-41... -

Page 197: Lpstop Broadcast Bus Cycle Timing, Bg Negated

A31–A0 $FFFFFFFE MISCELLANEOUS ATTRIBUTES TT1–TT0 SIZ1–SIZ0 WORD TM2–TM0 BS1–BS0 BS3–BS2 CIOUT D15–D0 DRIVE PST4–PST0 CLK MAY BE LPSTOP NO ALTERNATE MASTER ACTIVITY ALLOWED STOPPED LOW BROADCAST Figure 7-33. LPSTOP Broadcast Bus Cycle Timing, BG Negated 7-42 M68060 USER’S MANUAL MOTOROLA... -

Page 198: Lpstop Broadcast Bus Cycle Timing, Bg Asserted

A31–A0 $FFFFFFFE MISCELLANEOUS ATTRIBUTES TT1–TT0 SIZ1–SIZ0 WORD TM2–TM0 BS1–BS0 BS3–BS2 CIOUT D15–D0 DRIVE PST4–PST0 CLK MAY BE LPSTOP NO ALTERNATE MASTER ACTIVITY ALLOWED STOPPED LOW BROADCAST Figure 7-34. LPSTOP Broadcast Bus Cycle Timing, BG Asserted MOTOROLA M68060 USER’S MANUAL 7-43... -

Page 199: Exiting Lpstop Mode Flowchart

Figure 7-35. Exiting LPSTOP Mode Flowchart Note that the acknowledge termination ignore state capability is applicable to the LPSTOP broadcast cycle. If enabled, TA, TEA, and TRA are ignored for a user-programmed number of BCLK cycles. 7-44 M68060 USER’S MANUAL MOTOROLA... -

Page 200: Exiting Lpstop Mode Timing Diagram

TCI, TBI, AVEC SNOOP, BGR, MDIS, CDIS, CLA D31–D0 PST4–PST0 IPL2–IPL0 CLK READY FOR MORE EXCEPTION THAN 8 CLKS PROCESSING AND 2 BCLKS NO ALTERNATE MASTER ACTIVITY ALLOWED Figure 7-36. Exiting LPSTOP Mode Timing Diagram MOTOROLA M68060 USER’S MANUAL 7-45... -

Page 201: Termination Result Summary

2nd, 3rd, or 4th long word of a line transfer is interpreted as a bus error termination. This rule applies also for the second, third, and fourth long-word transfer on a line transfer that was burst inhibited. 7-46 M68060 USER’S MANUAL MOTOROLA... - Page 202 Although the fault address indicates the logical address of the write cycle that incurred the bus error, the write data information is not available in the access error stack. As such, this access error case is nonrecoverable unless the system is MOTOROLA M68060 USER’S MANUAL 7-47...

-

Page 203: Word Write Access Bus Cycle Terminated With Tea Timing

MC68060 before the retry operation with a snoop access during the arbitra- tion which invalidates the cache push, the processor does not initiate a retry operation. Fig- ure 7-39 illustrates a functional timing diagram for a retry of a read bus transfer. 7-48 M68060 USER’S MANUAL MOTOROLA... -

Page 204: Line Read Access Bus Cycle Terminated With Tea Timing

However, when in the native-MC68060 acknowledge termination mode, a retry termination signaled during the second, third, or fourth long-word transfers of a line burst bus cycle are ignored. MOTOROLA M68060 USER’S MANUAL 7-49... -

Page 205: Retry Read Bus Cycle Timing

If retrying a bus cycle that is part of a locked sequence of bus cycles, a relinquish and retry of the bus requires BGR be asserted along with BG negated to cause the processor to abort any following locked bus cycles that are a part of the locked sequence. 7-50 M68060 USER’S MANUAL MOTOROLA... -

Page 206: Line Write Retry Bus Cycle Timing

$1C until the processor is reset. Only an external reset operation can restart a halted processor. The halted processor releases the external bus by negating BR and forcing all outputs to a high-impedance state. MOTOROLA M68060 USER’S MANUAL 7-51... - Page 207 The MC68060 supports two bus arbitration protocols. These arbitration protocols are mutu- ally exclusive and must not be mixed in a system. An MC68040-style arbitration protocol is 7-52 M68060 USER’S MANUAL MOTOROLA...

- Page 208 Systems may use the BGR input to assign severity of the BG negation. For instance, if bus arbitration is used to allow for DRAM refresh, it is okay to ignore locked sequences and force the MC68060 to MOTOROLA M68060 USER’S MANUAL 7-53...

- Page 209 Figure 7-41 is a bus arbitration state diagram for the MC68040 bus arbitration protocol. Table 7-6 lists conditions that cause a change to and from the various states. Table 7-7 lists a summary of the bus conditions and states. 7-54 M68060 USER’S MANUAL MOTOROLA...

-

Page 210: Mc68040-Arbitration Protocol Transition Conditions

8) The processor does not require a valid acknowledge termination for snooped accesses. The only restriction is that a snoop cycle be performed at no more than a maximum rate of once every two BCLK cycles. This state diagram properly emulates this behavior. MOTOROLA M68060 USER’S MANUAL 7-55... -

Page 211: Mc68040-Arbitration Protocol State Description

However, in order for the processor to properly detect this boundary condition, it is imperative that the TS of all alternate bus masters be tied together with the processor’s TS signal 7-56 M68060 USER’S MANUAL MOTOROLA... -

Page 212: Mc68040-Arbitration Protocol State Diagram

= EXTERNAL BUS REQUEST PIN = INTERNAL BB SAMPLED AS INPUT BCLK = BB DRIVEN INTERNALLY BY MC68060 = EXTERNAL BB PIN BCLK = VIRTUAL BUS CLOCK DERIVED FROM CLK AND CLKEN Figure 7-41. MC68040-Arbitration Protocol State Diagram MOTOROLA M68060 USER’S MANUAL 7-57... - Page 213 BG and is ready to end usage of the bus. After the final termination acknowledgment of the final bus cycle when the MC68060 has lost bus owner- ship, the processor asserts BTT for a one BCLK period, negates BTT for a one BCLK period, 7-58 M68060 USER’S MANUAL MOTOROLA...

- Page 214 In this case, the MC68060 completes the sequence of atomic locked bus cycles, drives LOCK and LOCKE negated for one BCLK period during the clock when the address and other bus cycle attributes are idled, and in the next BCLK period, three-states LOCK MOTOROLA M68060 USER’S MANUAL 7-59...

- Page 215 LOCK and BGR, this can have the effect of preventing overlapped bus arbitration during locked sequences. By keeping LOCK asserted throughout the duration of a locked sequence, the last bus cycle of the sequence can be retried and still maintain the lock status. 7-60 M68060 USER’S MANUAL MOTOROLA...

- Page 216 MC68040-arbitration protocol with the exception that BB is no longer used as an input. As with the MC68040-arbitration protocol, the end tenure state is used to inform other bus masters the processor is relinquishing the bus. MOTOROLA M68060 USER’S MANUAL 7-61...

-

Page 217: Mc68060-Arbitration Protocol State Transition Conditions

8) The processor does not require a valid acknowledge termination for snooped accesses. The only restriction is that a snoop cycle be performed at no more than a maximum rate of once every two BCLK cycles. This state diagram prop- erly emulates this behavior. 7-62 M68060 USER’S MANUAL MOTOROLA... -

Page 218: Mc68060-Arbitration Protocol State Description

However, in order for the processor to properly detect this boundary condition, it is imperative that the TS of all alternate bus masters be tied together with the processor’s TS signal. MOTOROLA M68060 USER’S MANUAL 7-63... -

Page 219: Mc68060-Arbitration Protocol State Diagram

BTTI = INTERNAL BTT SAMPLED AS INPUT BTTO = BTT DRIVEN INTERNALLY BY MC68060 BCLK = EXTERNAL BTT PIN = VIRTUAL BUS CLOCK DERIVED FROM CLK AND CLKEN BCLK Figure 7-42. MC68060-Arbitration Protocol State Diagram 7-64 M68060 USER’S MANUAL MOTOROLA... - Page 220 If the branch prediction is incorrect and if the conditional branch results in a branch- not-taken, the previously issued branch-taken prefetch is then terminated since the prefetch MOTOROLA M68060 USER’S MANUAL 7-65...

- Page 221 BCLK period and is negated for one BCLK period during C10. BTT is then three-stated in C10. Further note that BB is only negated for one CLK (as opposed to BCLK) period before being three-stated, and the MC68040-arbitration protocol should not be used for full bus speed operation. 7-66 M68060 USER’S MANUAL MOTOROLA...

-

Page 222: Processor Bus Request Timing

Figure 7-46 illustrates the effect of BGR on bus arbitration activity during locked sequences. When BGR is asserted while BG is negated, locked sequences can be broken. Otherwise, the entire locked sequence of bus cycles are completed by the processor before relinquish- ing the bus. MOTOROLA M68060 USER’S MANUAL 7-67... -

Page 223: Arbitration During Relinquish And Retry Timing

Snooping can occur when the bus is granted to another bus master, and the MC68060 sees a TS assertion by the alternate master. If SNOOP is asserted, the processor registers the value of the A31–A0 and TT1 signals on the rising edge of BCLK in which TS is asserted. 7-68 M68060 USER’S MANUAL MOTOROLA... -

Page 224: Implicit Bus Ownership Arbitration Timing

MC68060 caches, the entry is invalidated regardless of the state of the R/W signal, transfer size, or whether or not the line has clean or dirty data. If SNOOP is negated, no snooping is done, and no lines in the caches are invalidated. MOTOROLA M68060 USER’S MANUAL 7-69... -

Page 225: Effect Of Bgr On Locked Sequences

The MC68060 does not require snooped bus cycles to be terminated with a legal transfer termination (TA, TEA, or TRA). The only requirement is that TS be asserted no more fre- quently than once every other BCLK edge. Figure 7-47 shows a snooped bus cycle. 7-70 M68060 USER’S MANUAL MOTOROLA... -

Page 226: Snooped Bus Cycle

RSTI is internally synchronized for two BCLKs before being used and must meet the specified MOTOROLA M68060 USER’S MANUAL 7-71... -

Page 227: Initial Power-On Reset Timing

BCLK in which RSTI is sampled low. These sig- nals should be driven to their normal levels before the end of the 27-CLK internal reset period. 7-72 M68060 USER’S MANUAL MOTOROLA... -

Page 228: Normal Reset Timing

RSTO signal to negate. RSTO can be logically ANDed with the external signal driving RSTI to derive a system reset signal that is asserted for both an external processor reset and execution of a RESET instruction. MOTOROLA M68060 USER’S MANUAL 7-73... -

Page 229: Data Bus Usage During Reset

For byte, word, or long-word transfers, the bus cycle ends when a valid termination is detected. For line transfer cycles after the first long-word transfer, the secondary ignore state count value is 7-74 M68060 USER’S MANUAL MOTOROLA... -

Page 230: Acknowledge Termination Ignore State Example

TA is asserted and recognized on the rising edge of C12. IGNORED IGNORED IGNORED IGNORED BCLK ADDRESS AND ATTRIBUTES D31–D0 READ PRIMARY IGNORE STATE COUNT = 1 READ SECONDARY IGNORE STATE COUNT = 1 Figure 7-51. Acknowledge Termination Ignore State Example MOTOROLA M68060 USER’S MANUAL 7-75... - Page 231 Figure 7- 52 shows an example of a line transfer cycle with this mode enabled. Read cycles are unaf- fected by this mode. 7-76 M68060 USER’S MANUAL MOTOROLA...

-

Page 232: Extra Data Write Hold Example

Bus Operation BCLK ADDRESS AND ATTRIBUTES D31–D0 DRIVE Figure 7-52. Extra Data Write Hold Example MOTOROLA M68060 USER’S MANUAL 7-77... - Page 233 SR. During the second step, the processor determines the vector number for the exception. For interrupts, the processor performs an interrupt acknowledge bus cycle to obtain the vector MOTOROLA M68060 USER’S MANUAL...

-

Page 234: General Exception Processing Flowchart

For all other exceptions, internal logic provides the vector number. This vector num- ber is used in the last step to calculate the address of the exception vector. Throughout this section, vector numbers are given in decimal notation. M68060 USER’S MANUAL MOTOROLA... -

Page 235: General Form Of Exception Stack Frame

Since the VBR provides the base address of the exception vector table, the exception vector table can be located anywhere in memory; it can even be dynamically relocated for each task that an operating system exe- cutes. MOTOROLA M68060 USER’S MANUAL... -

Page 236: Exception Vector Assignments

The MC68060 supports a 1024-byte vector table containing 256 exception vectors (see Table 8-1). Motorola defines the first 64 vectors and reserves the other 192 vectors for user- defined interrupt vectors. External devices can use vectors reserved for internal purposes at the discretion of the system designer. - Page 237 At that time, the bus error is signaled and exception pro- cessing is initiated. If a bus error is encountered during an instruction prefetch cycle, but the corresponding instruction is never executed due to a change-of-flow in the instruction stream, the bus error is discarded. MOTOROLA M68060 USER’S MANUAL...

- Page 238 The stack must be resident with correct protection in the direction of growth to ensure that exception stacking never has a bus error or internal access error. Memory pages allocated to the stack that are higher in memory than the current stack pointer can be nonresident M68060 USER’S MANUAL MOTOROLA...

- Page 239 A stack frame of type 0 is generated when a TRAP #n exception is taken. The saved value of the PC is the logical address of the instruction following the instruction that caused the trap. Instruction execution resumes at the address in the exception vector after the required instruction is prefetched. MOTOROLA M68060 USER’S MANUAL...

- Page 240 (bits 15–12) with $A. The A-line opcodes are user-reserved, and Motorola will not use any A-line instructions to extend the instruction set of any of Motor- ola’s processors. A stack frame of format 0 is generated when this exception is reported.

- Page 241 This exception is also taken when that opcode is executed. A stack frame of type 0 is gen- erated when this exception is taken. The stacked PC points to the logical address of the ille- gal instruction that caused the exception. MOTOROLA M68060 USER’S MANUAL...

- Page 242 The T-bit in the supervisor portion of the SR controls tracing. The state of the T-bit when an instruction begins execution determines whether the instruction generates a trace exception after the instruction completes. 8-10 M68060 USER’S MANUAL MOTOROLA...

- Page 243 8.2.8 Breakpoint Instruction Exception To provide increased debug capabilities in conjunction with a hardware emulator, the MC68060 provides a series of breakpoint instructions ($4848–$484F) which generate a special external bus cycle when executed. MOTOROLA M68060 USER’S MANUAL 8-11...

-

Page 244: Interrupt Levels And Mask Values

A level comparison also generates a level 7 interrupt if the request level and mask level are at 7 and the priority mask is then set to a lower level (as 8-12 M68060 USER’S MANUAL MOTOROLA... -

Page 245: Interrupt Recognition Examples

SR, sets the mode to supervisor, suppresses tracing, and sets the processor interrupt mask level to the level of the interrupt being serviced. The processor attempts to obtain a vector number from the MOTOROLA M68060 USER’S MANUAL 8-13... - Page 246 The reset exception does not flush the ATCs or invalidate entries in the instruction or data caches; it does not save the value of either the PC or the SR. If an access error or address 8-14 M68060 USER’S MANUAL MOTOROLA...

-

Page 247: Interrupt Exception Processing Flowchart

The processor halts and signals the double bus fault status on the processor status outputs ([PST4–PST0] = $1C). Execution of the reset instruction does not cause a reset exception, nor does it affect any internal registers except the PC. The execution of this MOTOROLA M68060 USER’S MANUAL 8-15... -

Page 248: Reset Exception Processing Flowchart