Table of Contents

Advertisement

Advertisement

Table of Contents

Summary of Contents for Motorola MVME2603-1121A

- Page 1 MVME2600 Series Single Board Computer Installation and Use V2600A/IH2...

- Page 2 Motorola, Inc. assumes no liability resulting from any omissions in this document, or from the use of the information obtained therein. Motorola reserves the right to revise this document and to make changes from time to time in the content hereof without obligation of Motorola to notify any person of such revision or changes.

- Page 3 Motorola symbol are registered trademarks of Motorola, Inc. AIXª is a trademark of IBM Corp. PowerPCª is a trademark of IBM Corp. and is used by Motorola with permission. All other products mentioned in this document are trademarks or registered trademarks of their respective holders.

- Page 4 Motorola, Inc. assumes no liability for the customer's failure to comply with these requirements. The safety precautions listed below represent warnings of certain dangers of which Motorola is aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

- Page 5 All Motorola PWBs (printed wiring boards) are manufactured by UL-recognized manufacturers, with a ßammability rating of 94V-0. This equipment generates, uses, and can radiate electro- magnetic energy. It may cause or be susceptible to electro-magnetic interference (EMI) if not installed and WARNING used in a cabinet with adequate EMI protection.

-

Page 7: Table Of Contents

Contents Chapter 1 Hardware Preparation and Installation Introduction ......................1-1 Equipment Required....................1-3 Overview of Startup Procedure .................1-4 Unpacking Instructions ..................1-5 Hardware ConÞguration..................1-5 MVME2603/2604 Base Board Preparation ............1-6 Cache Mode Control (J3) ................1-7 Flash Bank Selection (J10)................1-7 Serial Port 4 Receive Clock ConÞguration (J16) ........1-9 Serial Port 4 Transmit Clock ConÞguration (J17) ........ - Page 8 Chapter 2 Operating Instructions Introduction ......................2-1 Applying Power ....................2-1 ABORT Switch (S1) ..................2-2 RESET Switch (S2) ..................2-3 Front Panel Indicators (DS1 - DS6) ............. 2-4 Memory Maps ...................... 2-5 Processor Memory Map................2-5 Default Processor Memory Map 2-5 PCI Local Bus Memory Map................

- Page 9 Real-Time Clock/NVRAM/Timer Function ...........3-13 Programmable Timers.................3-14 Interval Timers 3-14 16-Bit Timers 3-15 Serial Communications Interface ..............3-15 Z8536 CIO Device 3-16 Base Module Feature Register ..............3-16 P2 Signal Multiplexing................3-17 ABORT Switch (S1)..................3-18 RESET Switch (S2) ..................3-19 Front Panel Indicators (DS1 - DS6)............3-19 Polyswitches (Resettable Fuses) ..............3-20...

- Page 10 CNFG - ConÞgure Board Information Block ........... 6-2 ENV - Set Environment..................6-3 ConÞguring the PPCBug Parameters ............6-3 ConÞguring the VMEbus Interface............6-12 Motorola Computer Group Documents ............A-1 ManufacturersÕ Documents ................A-2 Related SpeciÞcations..................A-6 Appendix B Specifications SpeciÞcations ......................B-1...

- Page 11 Interface Characteristics................C-8 Proper Grounding ....................C-9 Appendix D Troubleshooting CPU Boards: Solving Startup Problems Introduction ......................D-1 Glossary Abbreviations, Acronyms, and Terms to Know........... GL-1...

- Page 13 Figures Figure 1-1. MVME2603/2604 Base Board Block Diagram......1-2 Figure 1-2. MVME2603/2604 Switches, Headers, Connectors, Fuses, LEDs ......................1-10 Figure 1-3. MVME712M Connector and Header Locations ......1-16 Figure 1-4. J15 Clock Line ConÞguration............1-17 Figure 1-5. MVME712M Serial Port 1 DCE/DTE ConÞguration ....1-18 Figure 1-6.

- Page 15 Tables Table 1-1. VMEmodule/Transition Module Correspondence .......1-3 Table 1-2. Startup Overview ................1-4 Table 1-3. MVME712M Port/Jumper Correspondence ........1-17 Table 2-1. Processor Default View of the Memory Map .........2-6 Table 2-2. PCI Arbitration Assignments............2-9 Table 2-3. IBC DMA Channel Assignments............2-12 Table 2-4. Classes of Reset and Effectiveness ..........2-13 Table 3-1.

- Page 16 Table 5-2. Diagnostic Test Groups..............5-8 Table A-1. Motorola Computer Group Documents ........A-1 Table A-2. ManufacturersÕ Documents ............A-2 Table A-3. Related SpeciÞcations ..............A-6 Table B-1. MVME2603/2604 SpeciÞcations............B-1 Table C-1. EIA-232-D Interconnect Signals............C-3 Table C-2. EIA-232-D Interface Transmitter Characteristics ......

- Page 17 1Hardware Preparation and Installation Introduction This manual provides general information, hardware preparation and installation instructions, operating instructions, and a functional description of the MVME2603/2604 family of Single Board Computers. The MVME2603/2604 is a single-slot VMEmodule equipped with a PowerPCª Series microprocessor. The MVME2603 is equipped with a PowerPC 603 microprocessor;...

-

Page 18: Introduction

Introduction CLOCK DEBUG CONNECTOR MEMORY EXPANSION CONNECTORS GENERATOR L2 CACHE 256K FLASH FLASH 4MB or 8MB PROCESSOR SYSTEM MPC603/604 REGISTERS PHB & MPIC MEMORY CONTROLLER RAVEN ASIC FALCON CHIPSET 33MHz 32/64-BIT PCI LOCAL BUS ETHERNET SCSI VME BRIDGE W83C553 DEC21140 53C825A UNIVERSE REGISTERS... -

Page 19: Equipment Required

MVME712M or MVME761 transition modules. The following table shows the relationship between MVME2603/ 2604 model numbers and the applicable transition module. Table 1-1. VMEmodule/Transition Module Correspondence MVME761-Compatible Models MVME712-Compatible Models MVME2603-1121A MVME2603-2121A MVME2603-1131A MVME2603-2131A MVME2603-1141A MVME2603-2141A MVME2603-1151A... -

Page 20: Overview Of Startup Procedure

Overview of Startup Procedure In models of the MVME2603/2604 that are configured for MVME712M I/O mode, the pin assignments of VMEbus connector P2 are fully compatible with other transition modules of the MVME712 series. In MVME761-compatible models, certain signals are multiplexed through P2 for additional I/O capacity. Refer to Signal Multiplexing in Chapter 3 for details. -

Page 21: Unpacking Instructions

Hardware Preparation and Installation Table 1-2. Startup Overview (Continued) What you need to do... Refer to... On page... Note that the debugger Using the Debugger initializes the MVME2603/ You may also wish to obtain the PPCBug 2604. Firmware Package UserÕs Manual, listed in Appendix A, Related Documentation. -

Page 22: Mvme2603/2604 Base Board Preparation

MVME2603/2604 Base Board Preparation The MVME2603/2604 provides software control over most options: by setting bits in control registers after installing the module in a system, you can modify its configuration. (The MVME2603/2604 control registers are described in Chapter 3, and/or in the MVME2600 Series Single Board Computer Programmer's Reference Guide as listed under Related Documentation in Appendix A.) Some options, however, are not software-programmable. -

Page 23: Cache Mode Control (J3)

Hardware Preparation and Installation The MVME2603/2604 is factory tested and shipped with the configurations described in the following sections. The MVME2603/2604Õs required and factory-installed debug monitor, PPCBug, operates with those factory settings. Cache Mode Control (J3) 256KB of L2 cache memory is available on the MVME2603/2604. L2 cache operation is transparent to users, but its write-through mode is configurable via header J3 on older boards. - Page 24 MVME2603/2604 Base Board Preparation To enable Flash bank A (4MB or 8MB of firmware resident on soldered-in devices on the RAM200 mezzanine), place a jumper across header J10 pins 1 and 2. To enable Flash bank B (1MB of firmware located in sockets on the base board), place a jumper across header J10 pins 2 and 3.

- Page 25 Hardware Preparation and Installation Serial Port 4 Receive Clock Configuration (J16) In synchronous serial communications, you can configure Serial Port 4 on the MVME2603/2604 to use the clock signals provided by the RxC signal line. On MVME712M-compatible versions of the base board, header J16 configures port 4 to either drive or receive RxC.

-

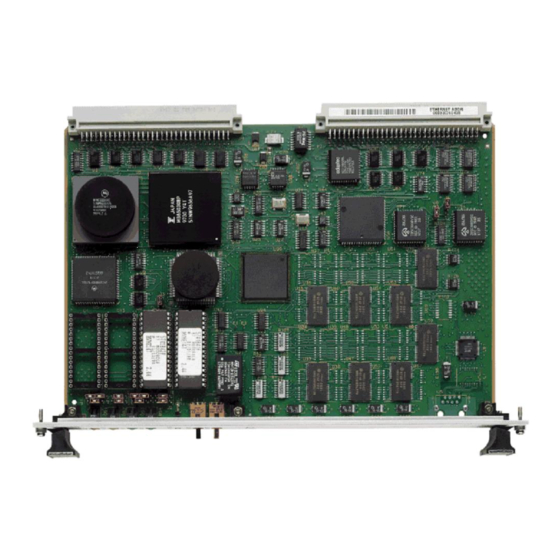

Page 26: Figure 1-2. Mvme2603/2604 Switches, Headers, Connectors, Fuses

MVME2603/2604 Base Board Preparation Figure 1-2. MVME2603/2604 Switches, Headers, Connectors, Fuses, LEDs 1-10... - Page 27 Hardware Preparation and Installation Serial Port 4 Transmit Clock Configuration (J17) In synchronous serial communications, you can configure Serial Port 4 on the MVME2603/2604 to use the clock signals provided by the TxC signal line. Header J17 configures port 4 to either drive or receive TxC.

-

Page 28: Serial Port 4 Transmit Clock Receiver Buffer Control (J20)

MVME2603/2604 Base Board Preparation Serial Port 4 Transmit Clock Receiver Buffer Control (J20) As described in other sections, a complete configuration of Serial Port 4 requires that you set the following jumper headers on the MVME2603/2604 or the transition module: J16 (Serial Port 4 receive clock configuration) on MVME712M-compatible versions of the base board J17 (Serial Port 4 transmit clock configuration) - Page 29 Hardware Preparation and Installation Serial Port 3 Transmit Clock Configuration (J18) In synchronous serial communications using the MVME761 transition module, you can configure Serial Port 3 on the MVME2603/2604 to use the clock signals provided by the TxC signal line. On MVME761-compatible versions of the base board, header J18 configures port 3 to either drive or receive TxC.

-

Page 30: System Controller Selection (J22)

MVME2603/2604 Base Board Preparation System Controller Selection (J22) The MVME2603/2604 is factory-configured as a VMEbus system controller by jumper header J22. If you select the ÔÔautomaticÕÕ system controller function by placing a jumper on J22 pins 2 and 3, the MVME2603/2604 determines whether it is the system controller by its position on the bus. -

Page 31: Mvme712M Transition Module Preparation

Hardware Preparation and Installation MVME712M Transition Module Preparation The MVME712M transition module (Figure 1-3) and P2 adapter board are used in conjunction with the following models of the MVME2603/2604 base board: MVME2603-2121A MVME2604-2121A MVME2603-2131A MVME2604-2131A MVME2603-2141A MVME2604-2141A MVME2603-2151A MVME2604-2151A MVME2603-2161A MVME2604-2161A The features of the MVME712M include: A parallel printer port... -

Page 32: Figure 1-3. Mvme712M Connector And Header Locations

MVME712M Transition Module Preparation MVME712M Figure 1-3. MVME712M Connector and Header Locations 1-16... -

Page 33: Serial Ports 1-4 Dce/Dte Conþguration

Hardware Preparation and Installation Serial Ports 1-4 DCE/DTE Configuration Serial ports 1 through 4 are configurable as modems (DCE) for connection to terminals, or as terminals (DTE) for connection to modems. The MVME712M is shipped with the serial ports configured for DTE operation. Serial port DCE/DTE configuration is accomplished by positioning jumpers on one of two headers per port. - Page 34 MVME712M Transition Module Preparation MVME2603/2604 P2 ADAPTER 64-PIN MVME712M BOARD CABLE MODULE PC87308 SOUT1 RTS1# DTR1# +12V SIN1 CTS1# DCD1# +12V DSR1# R11# 11551.00 9609 (1-8) MVME2603/2604 P2 ADAPTER 64-PIN MVME712M BOARD CABLE MODULE PC87308 SOUT1 RTS1# DTR1# +12V SIN1 CTS1# DCD1# DSR1#...

-

Page 35: Hardware Preparation And Installation

Hardware Preparation and Installation MVME2603/2604 P2 ADAPTER 64-PIN MVME712M BOARD CABLE MODULE PC87308 SOUT2 RTS2# DTR2# SIN2 CTS2# DCD2# DSR2# +12V R12# 11551.00 9609 (3-8) MVME2603/2604 P2 ADAPTER 64-PIN MVME712M BOARD CABLE MODULE PC87308 SOUT2 RTS2# DTR2# SIN2 CTS2# DCD2# DSR2# R12# 11551.00 9609 (4-8) -

Page 36: Figure 1-7. Mvme712M Serial Port 3 Dce

MVME712M Transition Module Preparation MVME2603/2604 64-PIN MVME712M ADAPTER CABLE MODULE Z85230 TXDA RTSA# DCDA# RXDA CTSA# TRXCA# RTXCA# Z8536 DTR3# LLB3# RLB3# DSR3# +12V R13# TM3# NOTE : J18 OPEN 11551.00 9609 (5-8) Figure 1-7. MVME712M Serial Port 3 DCE Configuration 1-20... - Page 37 Hardware Preparation and Installation MVME2603/2604 64-PIN MVME712M ADAPTER CABLE MODULE DB25 Z85230 TXDA RTSA# DCDA# RXDA CTSA# TRXCA# RTXCA# Z8536 DTR3# LLB3# RLB3# DSR3# R13# TM3# NOTE : J18 OPEN 11551.00 9609 (6-8) Figure 1-8. MVME712M Serial Port 3 DTE Configuration 1-21...

-

Page 38: Figure 1-9. Mvme712M Serial Port 4 Dce

MVME712M Transition Module Preparation MVME2603/2604 64-PIN MVME712M ADAPTER CABLE MODULE DB25 Z85230 TXDB RTSB# DCDB# RXDB CTSB# TXCI RXCI TXCO TRXCB RTXCB Z8536 DTR4# LLB4# RLB4# DSR4# +12V R14# TM4# NOTE : J20 OPEN J16 1-2 J17 1-2 11551.00 9609 (7-8) Figure 1-9. -

Page 39: Figure 1-10. Mvme712M Serial Port 4 Dte

Hardware Preparation and Installation MVME2603/2604 64-PIN MVME712M ADAPTER CABLE MODULE DB25 Z85230 TXDB RTSB# DCDB# RXDB CTSB# TXCI RXCI TXCO TRXCB RTXCB Z8536 DTR4# LLB4# RLB4# DSR4# R14# TM4# NOTE : J20 1-2 J16 2-3 J17 2-3 11551.00 9609 (8-8) Figure 1-10. -

Page 40: P2 Adapter Preparation

1Hardware Preparation and Installation P2 Adapter Preparation Preparation of the P2 adapter for the MVME712M consists of removing or installing the SCSI terminating resistors. Figure 1-11 illustrates the location of the resistors, fuse, and connectors. For further information on the preparation of the transition module and the P2 adapter, refer to the userÕs manual for the MVME712M (listed in the Related Documentation appendix) as necessary. -

Page 41: Mvme761 Transition Module Preparation

Hardware Preparation and Installation MVME761 Transition Module Preparation The MVME761 transition module (Figure 1-12) and P2 adapter board are used in conjunction with the following models of the MVME2603/2604 base board: MVME2603-1121A MVME2604-1121A MVME2603-1131A MVME2604-1131A MVME2603-1141A MVME2604-1141A MVME2603-1151A MVME2604-1151A MVME2603-1161A... -

Page 42: Figure 1-12. Mvme761 Connector And Header

MVME761 Transition Module Preparation MVME 761-001 Figure 1-12. MVME761 Connector and Header Locations 1-26... -

Page 43: Serial Ports 1 And 2

Hardware Preparation and Installation Serial Ports 1 and 2 On MVME761-compatible models of the MVME2603/2604 base board, the asynchronous serial ports (Serial Ports 1 and 2) are configured permanently as data circuit-terminating equipment (DCE). The port configuration is illustrated in Figure 1-14. - Page 44 MVME761 Transition Module Preparation Headers J2 and J3 are used to configure Serial Port 3 and Serial Port 4, respectively, in tandem with SIM selection. With the jumper in position 1-2, the port is configured as a DTE. With the jumper in position 2-3, the port is configured as a DCE.

-

Page 45: Figure 1-13. Mvme761 Serial Ports 1 And 2 (Dce Only)

Hardware Preparation and Installation MVME2603/2604 MVME761 SOUT1 RTS1# DTR1# SIN1 COM1 CTS1# DSR1# DCD1# RI1# PC87308 P2/P2MX SOUT2 RTS2# DTR2# SIN2 CTS2# COM2 DSR2# DCD2# RI2# 11552.00 9609 (1-3) Figure 1-13. MVME761 Serial Ports 1 and 2 (DCE Only) 1-29... -

Page 46: Figure 1-14. Mvme761 Serial Ports 3 And 4 Dce

MVME761 Transition Module Preparation MVME3600 SERIES MVME761 Z85230 SCC HD26 EIA232-DCE SIM RTS# CTS# DCD# J2/J3 TRXC RTXC P2/P2MX Z8536 CIO DTR# LLB# RLB# DSR# 11552.00 9802 (2-5) Figure 1-14. MVME761 Serial Ports 3 and 4 DCE Configuration 1-30... - Page 47 Hardware Preparation and Installation MVME2603/2604 SERIES MVME761 Z85230 SCC HD26 EIA232-DTE SIM RTS# CTS# DCD# J2/J3 TRXC RTXC P2/P2MX Z8536 CIO DTR# LLB# RLB# DSR# 11552.00 9802 (4-5) Figure 1-15. MVME761 Serial Ports 3 and 4 DTE Configuration 1-31...

-

Page 48: P2 Adapter Preparation (Three-Row)

MVME761 Transition Module Preparation P2 Adapter Preparation (Three-Row) The P2 adapter for the MVME761 transition module routes the synchronous and asynchronous serial, parallel, and Ethernet signals to the MVME761. The P2 adapter also has a 50-pin female connector (J2) that carries 8-bit SCSI signals from the MVME2603/2604. -

Page 49: Figure 1-16. Mvme761 P2 Adapter (Three-Row) Component Placement

Hardware Preparation and Installation For further information on the preparation of the transition module and the P2 adapter, refer to the userÕs manual for the MVME761 (listed in the Related Documentation appendix) as necessary. 1933 9610 Figure 1-16. MVME761 P2 Adapter (Three-Row) Component Placement 1-33... -

Page 50: P2 Adapter Preparation (Five-Row)

MVME761 Transition Module Preparation P2 Adapter Preparation (Five-Row) The MVME761 transition module uses a five-row P2 adapter to transfer the synchronous and asynchronous serial, parallel, and Ethernet signals to and from the MVME2600 series VMEmodule. The P2 adapter has a 68-pin female connector (J1) that carries 16-bit SCSI signals from the MVME2600. -

Page 51: Hardware Installation

ESD Precautions Motorola strongly recommends that you use an antistatic wrist strap Use ESD and a conductive foam pad when installing or upgrading a system. Electronic components, such as disk drives, computer boards, and memory modules, can be extremely sensitive to ESD. -

Page 52: Ram200 Memory Mezzanine Installation

RAM200 Memory Mezzanine Installation RAM200 Memory Mezzanine Installation The RAM200 DRAM mezzanine mounts on top of the MVME2603/2604 base board. To upgrade or install a RAM200 mezzanine, refer to Figure 1-18 and proceed as follows: 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. -

Page 53: Figure 1-18. Ram200 Placement On Mvme2603/2604

Hardware Preparation and Installation 4. Place the RAM200 mezzanine module on top of the base board. Connector J9 on the underside of the RAM200 should connect smoothly with the corresponding connector J7 on the MVME2603/2604. 11661.00 9611 (2-3) Figure 1-18. RAM200 Placement on MVME2603/2604 5. -

Page 54: Pmc Module Installation

PMC Module Installation PMC Module Installation PCI mezzanine card (PMC) modules mount beside the RAM200 mezzanine on top of the MVME2603/2604 base board. To install a PMC module, refer to Figure 1-19 and proceed as follows: 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. -

Page 55: Figure 1-19. Pmc Module Placement On

Hardware Preparation and Installation 4. Remove the PCI filler from the front panel. 11661.00 9611 (3-3) Figure 1-19. PMC Module Placement on MVME2603/2604 5. Slide the edge connector of the PMC module into the front panel opening from behind and place the PMC module on top of the base board. -

Page 56: Pmc Carrier Board Installation

PMC Carrier Board Installation PMC Carrier Board Installation PCI mezzanine card (PMC) carrier boards mount above the RAM200 mezzanine and (if installed) PMC module on the MVME2603/2604 base board. To install a PMC carrier board for additional PCI expansion, refer to Figure 1-20 and proceed as follows:... -

Page 57: Figure 1-20. Pmc Carrier Board Placement On Mvme2603/2604

Hardware Preparation and Installation 11661.00 9611 (1-3) Figure 1-20. PMC Carrier Board Placement on MVME2603/2604 5. Remove the LED module screw located at the upper front corner of the base board. Install a short (0.394 inch) standoff in its place. 1-41... -

Page 58: Mvme2603/2604 Vmemodule Installation

MVME2603/2604 VMEmodule Installation 6. At the other three corners of the base board, install long (0.737 inch) standoffs. 7. Place the PMC carrier board on top of the base board. The connector on the underside of the carrier board should connect smoothly with the corresponding connector J5 (located between P1 and P2) on the MVME2603/2604. - Page 59 Hardware Preparation and Installation Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting. Warning 3. Remove the filler panel from the card slot where you are going to install the MVME2603/2604. Ð...

-

Page 60: Mvme712M Transition Module Installation

MVME712M Transition Module Installation Note Some VME backplanes (e.g., those used in Motorola ÔÔModular ChassisÕÕ systems) have an autojumpering feature for automatic propagation of the IACK and BG signals. Step 6 does not apply to such backplane designs. 7. If necessary, install an MVME712M or MVME761 transition module and cable it to the MVME2603/2604 as described in the following sections of this document. - Page 61 Hardware Preparation and Installation Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting. Warning 3. Remove the filler panel(s) from the appropriate card slot(s) at the front or rear of the chassis. (You may need to shift other modules in the chassis to allow space for the MVME712M, which has a double-wide front panel.) 4.

- Page 62 AC or DC power source, and turn the equipment power on. Not all peripheral cables are provided with the Note MVME712M; you may need to fabricate or purchase certain cables. (To minimize radiation, Motorola recommends shielded cable for peripheral connections where possible.) 1-46...

-

Page 63: Figure 1-21. Mvme712M/Mvme2603/2604 Cable Connections

Hardware Preparation and Installation TERMINATORS SCSI INSTALLED DEVICE SCSI DEVICE MVME712M MVME2600 50-CONDUCTOR CABLE 64-CONDUCTOR CABLE P2 ADAPTER TERMINATORS TERMINATORS REMOVED INSTALLED ENCLOSURE BOUNDARY cb2349301 Figure 1-21. MVME712M/MVME2603/2604 Cable Connections 1-47... -

Page 64: Mvme761 Transition Module Installation

MVME761 Transition Module Installation MVME761 Transition Module Installation This section applies to MVME761-compatible models of the MVME2603/2604 VMEmodule. With the MVME2603/2604 installed, refer to Figure 1-22 and proceed as follows to install an MVME761 transition module: 1. Attach an ESD strap to your wrist. Attach the other end of the ESD strap to the chassis as a ground. -

Page 65: Figure 1-22. Mvme761/Mvme2603/2604 Cable Connections

Hardware Preparation and Installation MVME761-001 MVME2600/MVME3600 64-CONDUCTOR CABLE P2 ADAPTER ENCLOSURE BOUNDARY 11635.00 9610 Figure 1-22. MVME761/MVME2603/2604 Cable Connections 5. Route the 64-conductor cable furnished with the MVME761 from J3 on the P2 adapter board to P2 on the transition module. -

Page 66: System Considerations

Note Not all peripheral cables are provided with the MVME761; you may need to fabricate or purchase certain cables. (To minimize radiation, Motorola recommends shielded cable for peripheral connections where possible.) System Considerations The MVME2603/2604 draws power from VMEbus backplane connectors P1 and P2. - Page 67 Hardware Preparation and Installation address ranges indicated in Chapter 2. D8 and/or D16 devices in the system must be handled by the PowerPCª processor software. Refer to the memory maps in Chapter 2. The MVME2603/2604 contains shared onboard DRAM (and, optionally, secondary cache memory) whose base address is software-selectable.

-

Page 68: Mvme2603/2604 Vmemodule

System Considerations MVME2603/2604 VMEmodule The MVME2603/2604 VMEmodule furnishes +12Vdc and (in MVME761 I/O mode) Ð12Vdc power to the transition module through polyswitches (resettable fuses) R34 and R28 respectively. These voltage sources power the serial port drivers and any LAN transceivers connected to the transition module. Fused +5Vdc power is supplied to the base boardÕs keyboard and mouse connectors through polyswitch R30 and to the 14-pin combined LED-mezzanine/remote-reset connector, J1. - Page 69 Hardware Preparation and Installation The MVME2603/2604 base board supplies a signal SPEAKER_OUT to the 14-pin combined LED-mezzanine/remote-reset connector, J1. When J1 is used as a remote reset connector with the LED mezzanine removed, the signal can be cabled to an SPEAKER_OUT external speaker.

- Page 70 System Considerations 1-54...

-

Page 71: Introduction

2Operating Instructions Introduction This chapter supplies information for use of the MVME2603/2604 family of Single Board Computers in a system configuration. Here you will find the power-up procedure and descriptions of the switches and LEDs, memory maps, and software initialization. Applying Power After you have verified that all necessary hardware preparation has been done, that all connections have been made correctly, and that... -

Page 72: Abort Switch (S1)

Applying Power STARTUP SYSTEM INITIALIZATION CONSOLE DETECTION RUN SELFTESTS (IF ENABLED) AUTOBOOT (IF ENABLED) OPERATING SYSTEM 11734.00 9702 Figure 2-1. PPCBug System Startup The MVME2603/2604 front panel has switches ABORT RESET and six LED (light-emitting diode) status indicators ( ). The switches and LEDs are mounted on an LED mezzanine board that plugs into the base board. -

Page 73: Reset Switch (S2)

Operating Instructions line IRQ8 ∗ . The signal is also available at pin PB7 of the Z8536 CIO device, which handles various status signals, serial I/O lines, and counters. The interrupter connected to the switch is an edge-sensitive ABORT circuit, filtered to remove switch bounce. RESET Switch (S2) switch resets all onboard devices;... -

Page 74: Front Panel Indicators (Ds1 - Ds6)

Applying Power Front Panel Indicators (DS1 - DS6) There are six LEDs on the MVME2603/2604 front panel: , and (DS1, yellow). Checkstop; driven by the MPC603/604 status lines on the MVME2603/2604. Lights when a halt condition from the processor is detected. (DS2, yellow). -

Page 75: Memory Maps

Operating Instructions Memory Maps There are three points of view for memory maps: The mapping of all resources as viewed by the processor (MPU bus memory map) The mapping of onboard resources as viewed by PCI local bus masters (PCI bus memory map) The mapping of onboard resources as viewed by VMEbus masters (VMEbus memory map) The following sections give a general description of the... -

Page 76: Pci Local Bus Memory Map

Memory Maps Table 2-1. Processor Default View of the Memory Map Processor Address Size DeÞnition Notes Start 00000000 7FFFFFFF Not Mapped 80000000 8001FFFF 128KB PCI/ISA I/O Space 80020000 FEF7FFFF 2GB-16MB-640KB Not Mapped FEF80000 FEF8FFFF 64KB Falcon Registers FEF90000 FEFEFFFF 384KB Not Mapped FEFF0000 FEFFFFFF... -

Page 77: Vmebus Memory Map

Operating Instructions For detailed PCI memory maps, including suggested CHRP- and PREP-compatible memory maps, refer to the MVME2600 Series Single Board Computer ProgrammerÕs Reference Guide (part number V2600A/PG). VMEbus Memory Map The VMEbus is programmable. Like other parts of the MVME2603/2604 memory map, the mapping of local resources as viewed by VMEbus masters varies among applications. -

Page 78: Figure 2-2. Vmebus Master Mapping

Programming Considerations VMEBUS PROCESSOR PCI MEMORY ONBOARD MEMORY PROGRAMMABLE SPACE NOTE 2 NOTE 1 PCI MEMORY SPACE VME A24 VME A16 NOTE 3 VME A24 VME A16 NOTE 1 VME A24 PCI/ISA MEMORY SPACE VME A16 VME A24 I/O SPACE VME A16 RESOURCES NOTES:... -

Page 79: Pci Arbitration

Operating Instructions PCI Arbitration There are 7 potential PCI bus masters on the MVME2603/2604 single-board computer: Raven ASIC (MPU/PCI bus bridge controller) Winbond W83C553 PIB (PCI/ISA bus bridge controller) DECchip 21140 Ethernet controller SCSI controller SYM53C825A Universe ASIC (PCI/VME bus bridge controller) PMC Slot 1 (PCI mezzanine card) PMC Slot 2 (PCI expansion) The Winbond W83C553 PIB device supplies the PCI arbitration... -

Page 80: Interrupt Handling

Programming Considerations Interrupt Handling The Raven ASIC, which controls PHB (PCI Host Bridge) MPU/local bus interface functions on the MVME2603/2604, performs interrupt handling as well. Sources of interrupts may be any of the following: The Raven ASIC itself (timer interrupts or transfer error interrupts) The processor (processor self-interrupts) The Falcon chip set (memory error interrupts) -

Page 81: Figure 2-3. Mvme2603/Mvme2604 Interrupt Architecture

Operating Instructions INT_ Processor (8529 Pair) MCP_ RavenMPIC SERR_& PERR_ PCI Interrupts ISA Interrupts 11559.00 9609 Figure 2-3. MVME2603/MVME2604 Interrupt Architecture 2-11... -

Page 82: Dma Channels

Programming Considerations DMA Channels The PIB supports seven DMA channels. Channels 0 through 3 support 8-bit DMA devices. Channels 5 through 7 are dedicated to 16-bit DMA devices. The channels are allocated as follows: Table 2-3. IBC DMA Channel Assignments IBC Label Controller DMA Assignment... -

Page 83: Endian Issues

Operating Instructions 6. The VMEbus ∗ signal SYSRESET 7. VMEbus Reset sources from the Universe ASIC (PCI/VME bus bridge controller): the System Software reset, Local Software Reset, and VME CSR Reset functions The following table shows which devices are affected by the various types of resets. -

Page 84: Processor/Memory Domain

Programming Considerations Processor/Memory Domain The MPC603/604 processor can operate in both big-endian and little-endian mode. However, it always treats the external processor/memory bus as big-endian by performing address rearrangement and reordering when running in little-endian mode. The MPC registers in the Raven MPU/PCI bus bridge controller ASIC and the Falcon memory controller chip set, as well as DRAM, ROM/Flash, and system registers, always appear as big-endian. -

Page 85: Vmebus Domain

Operating Instructions PCI and Ethernet Ethernet is also byte-stream-oriented; the byte having the lowest address in memory is the first one to be transferred regardless of the endian mode. Since the Raven maintains address invariance in both little-endian and big-endian mode, no endian issues should arise for Ethernet data. - Page 86 Programming Considerations 2-16...

-

Page 87: Introduction

3Functional Description Introduction This chapter describes the MVME2603/2604 single-board computer on a block diagram level. The General Description provides an overview of the MVME2603/2604, followed by a detailed description of several blocks of circuitry. Figure 3-1 shows a block diagram of the overall board architecture. Detailed descriptions of other MVME2603/2604 blocks, including programmable registers in the ASICs and peripheral chips, can be found in the ProgrammerÕs Reference Guide (part number... - Page 88 Features Table 3-1. MVME2603/2604 Features (Continued) Feature Description Four programmable 16-bit timers (one in S82378ZB ISA bridge; Tick timers three in Z8536 CIO device) Watchdog timer Provided in SGS-Thomson M48T59 Software interrupt handling via Raven (PCI-MPU bridge) and Interrupts Winbond (PCI-ISA bridge) controllers VME I/O VMEbus P2 connector MVME712M-compatible models: 3 async ports, 1 sync/async port...

-

Page 89: General Description

Functional Description Table 3-1. MVME2603/2604 Features (Continued) Feature Description VMEbus system controller functions VMEbus-to-local-bus interface (A24/A32, D8/D16/D32/block transfer [D8/D16/D32/D64]) Local-bus-to-VMEbus interface (A16/A24/A32, D8/D16/D32) VMEbus interface VMEbus interrupter VMEbus interrupt handler Global control/status register for interprocessor communications DMA for fast local memory/VMEbus transfers (A16/A24/A32, D16/D32/D64) General Description The MVME2603/2604 is a VMEmodule single-board computer... - Page 90 General Description Mode), graphics, Ethernet, or SCSI ports. The base board supports PMC front panel I/O. There is also provision for additional expansion via a PMC carrier board.

-

Page 91: Block Diagram

Functional Description Block Diagram Figure 3-1 is a block diagram of the MVME2603/2604Õs overall architecture. PS/2 Floppy Processor L2 Cache Parallel Keyboard Mouse Async Serial 60X System Bus ISA SIO Sync Serial Falcon Dram Falcon ISA Local Resource Bus FLASH NVRAM Raven ISA CSR... -

Page 92: Scsi Interface

Block Diagram SCSI Interface The MVME2603/2604 VMEmodule supports mass storage subsystems through the industry-standard SCSI bus. These subsystems may include hard and floppy disk drives, streaming tape drives, and other mass storage devices. The SCSI interface is implemented using the Symbios 53C825A SCSI I/O controller at a clock speed of 40MHz. -

Page 93: Ethernet Interface

Functional Description Ethernet Interface The MVME2603/2604 VMEmodule uses Digital EquipmentÕs DECchip 21140 PCI Fast Ethernet LAN controller to implement an Ethernet interface that supports both AUI (via MVME712M) and 10Base-T/100Base-TX (via MVME761) connections. The balanced differential transceiver lines are coupled via on-board transformers. -

Page 94: Pci Mezzanine Interface

Block Diagram map description in the MVME2600 Series Single Board Computer Programmer's Reference Guide for detailed programming information. PCI Mezzanine Interface A key feature of the MVME2603/2604 family is the PCI (Peripheral Component Interconnect) bus. In addition to the on-board local bus devices (SCSI, Ethernet, graphics, etc.), the PCI bus supports an industry-standard mezzanine interface, IEEE P1386.1 PMC (PCI Mezzanine Card). -

Page 95: Vmebus Interface

Functional Description Refer to Chapter 4 for the pin assignments of the PMC connectors. For detailed programming information, refer to the PCI bus descriptions in the MVME2603/2604 Programmer's Reference Guide and to the user documentation for the PMC modules you intend to use. - Page 96 Block Diagram Ð IEEE1284 bidirectional parallel port in MVME761- compatible models Floppy disk drive support via drive/power connector J4 Keyboard and mouse interface via circular DIN connectors J6 and J8 3-10...

-

Page 97: Asynchronous Serial Ports

Functional Description Asynchronous Serial Ports The two asynchronous ports provided by the ISASIO device employ TTL-level signals that are buffered through EIA-232-D drivers and receivers and routed to the P2 connector. Hardware initializes the two serial ports as COM1 and COM2 with ISA I/O base addresses of $3F8 and $2F8 respectively. -

Page 98: Disk Drive Controller

Block Diagram Disk Drive Controller The ISASIO device incorporates a PS/2-compatible low- and high- density disk drive controller for use with an optional external disk drive. The drive interfaces with the ISASIO controller via base board connector J4, which relays both power and control signals. The ISASIO disk drive controller is compatible with the DP8473, 765A, and N82077 devices commonly used to implement floppy disk controllers. -

Page 99: Real-Time Clock/Nvram/Timer Function

Functional Description The PIB controller provides the following functions: PCI bus arbitration for: Ð ISA (Industry Standard Architecture) bus DMA Ð The PHB (PCI Host Bridge) MPU/local bus interface function, implemented by the Raven ASIC Ð All on-board PCI devices Ð... -

Page 100: Programmable Timers

Block Diagram A 28-pin 330mil SO device containing the real-time clock, the oscillator, power failure detection circuitry, timer logic, 8KB of static RAM, and gold-plated sockets for a battery A SNAPHAT battery housing a crystal along with the battery The SNAPHAT battery package is mounted on top of the M48T59/T559 device. -

Page 101: 16-Bit Timers

Functional Description Counter 2 provides the tone for the speaker output function on the PIB controller (the signal which can be SPEAKER_OUT cabled to an external speaker via the remote reset connector). The interval timers use the OSC clock input as their clock source. The MVME2603/2604 drives the OSC pin with a 14.31818MHz clock source. -

Page 102: Z8536 Cio Device

Block Diagram source. Interrupt request levels are programmed via the PIB controller. Refer to the Z85230 data sheet and to the MVME2603/ MVME2604 Programmer's Reference Guide for further information. Z8536 CIO Device The Z8536 CIO device complements the Z85230 ESCC by supplying modem control lines not provided by the Z85230 ESCC. -

Page 103: P2 Signal Multiplexing

Functional Description ∗ VMEbus present. If set, there is no VMEbus interface. If VMEP cleared, the VMEbus interface is supported. ∗ Ethernet present. If set, no Ethernet transceiver interface LANP is installed. If cleared, there is on-board Ethernet support. ∗ SCSI present. -

Page 104: Abort Switch (S1)

Block Diagram Table 3-2. P2 Multiplexing Sequence MXDO (From Base Board) MXDI (From MVME761) Time Slot Signal Name Time Slot Signal Name RTS3 CTS3 DTR3 DSR3/MID1 LLB3/MODSEL DCD3 RLB3 TM3/MID0 RTS4 DTR4 CTS4 LLB4 DSR4/MID3 RLB4 DCD4 ∗ IDREQ TM4/MID2 DTR1 DTR2 Reserved... -

Page 105: Reset Switch (S2)

Functional Description RESET Switch (S2) switch is located on the LED mezzanine. The RESET RESET switch resets all onboard devices; it also drives a ∗ signal if SYSRESET the MVME2603/2604 is the system controller. Front Panel Indicators (DS1 - DS6) There are six LEDs on the MVME2603/2604 front panel: , and (DS1, yellow). -

Page 106: Polyswitches (Resettable Fuses)

Block Diagram Polyswitches (Resettable Fuses) The MVME2603/2604 base board draws fused +5Vdc, +12Vdc, and Ð12Vdc power from the VMEbus backplane through connectors P1 and P2. The 3.3Vdc and the core processor voltage power is supplied by the on-board +5Vdc. The following table lists the fuses with the voltages they protect. -

Page 107: Speaker Control

Functional Description module, the green LED on the module illuminates when SCSI SCSI terminator power is available. If the LED on the transition SCSI module flickers during SCSI bus operation, check fuse F1 on the P2 adapter board. Because any device on the SCSI bus can provide Note , and because the LED monitors the status... -

Page 108: Flash Memory

Block Diagram The PowerPC 603 is a 64-bit processor with 32KB on-chip cache (16KB data cache and 16KB instruction cache). The PowerPC 604 is a 64-bit processor with 32 KB on-chip cache (16KB data cache and 16KB instruction cache). The Raven bridge controller ASIC provides the bridge between the PowerPC microprocessor bus and the PCI local bus. -

Page 109: Ram200 Memory Module

Functional Description RAM200 Memory Module The RAM200 is the ECC DRAM memory mezzanine module that (together with an LED mezzanine and an optional PCI mezzanine card) plugs into the base board to make a complete MVME2603 or MVME2604 single-board computer. See Figure 1-18. -

Page 110: Mvme761 Transition Module

SCSI, and Ethernet signals to the MVME712M MVME761 Transition Module The MVME761 transition module (Figure 1-12) and P2 adapter board are used in conjunction with the following models of the MVME2603/2604 base board: MVME2603-1121A MVME2604-1121A MVME2603-1131A MVME2604-1131A MVME2603-1141A MVME2604-1141A MVME2603-1151A... -

Page 111: Serial Interface Modules

Functional Description Two synchronous serial ports ( on the SERIAL 3 SERIAL 4 front panel), configurable for EIA-232-D, EIA-530, V.35, or X.21 protocols Two 60-pin Serial Interface Module (SIM) connectors Serial Interface Modules The synchronous serial ports on the MVME761 are configurable via serial interface modules (SIMs), used in conjunction with the appropriate jumper settings on the transition module and base board. - Page 112 Block Diagram 3-26...

-

Page 113: Mvme2603/2604 Connectors

4Connector Pin Assignments MVME2603/2604 Connectors This chapter summarizes the pin assignments for the following groups of interconnect signals for the MVME2603/2604: Connectors with pin assignments common to MVME712M- as well as MVME761-compatible versions of the base board Connector Table LED Mezzanine connector J1 Debug connector J2 Floppy/LED connector J4 PCI Expansion connector J5... - Page 114 MVME2603/2604 Connectors Connectors with pin assignments specific to MVME761- compatible versions of the base board Connector Table VMEbus connector P2 4-15 Serial Ports 1 and 2 (at MVME761) 4-16 Serial Ports 3 and 4 (at MVME761) 4-17 Parallel I/O connector (at MVME761) 4-18 Ethernet 10Base-T/100Base-TX connector 4-19...

-

Page 115: Common Connectors

Connector Pin Assignments Common Connectors The following tables describe connectors used with the same pin assignments by MVME712M- as well as MVME761-compatible versions of the base board. LED Mezzanine Connector J1 A 14-pin connector (J1 on the base board) supplies the interface between the base board and the LED mezzanine module. -

Page 116: Table 4-2. Debug Connector

Common Connectors Table 4-2. Debug Connector PA10 PA11 PA12 PA13 PA14 PA15 PA16 PA17 PA18 PA19 PA20 PA21 PA22 PA23 PA24 PA25 PA26 PA27 PA28 PA29 PA30 PA31 PA_PAR0 PA_PAR1 PA_PAR2 PA_PAR3 ∗ ∗ RSRV PD10 PD11 PD12 PD13 PD14 PD15 PD16 PD17... - Page 117 Connector Pin Assignments Table 4-2. Debug Connector (Continued) PD38 PD39 PD40 PD41 PD42 PD43 PD44 PD45 PD46 PD47 PD48 PD49 PA50 PD51 PD52 PD53 PD54 PD55 PD56 PD57 PD58 PD59 PD60 PD61 PD62 PD63 PDPAR0 PDPAR1 PDPAR2 PDPAR3 PDPAR4 PDPAR5 PDPAR6 PDPAR7 No Connection...

- Page 118 Common Connectors Table 4-2. Debug Connector (Continued) ∗ ∗ L2ADSC IBCINT ∗ ∗ L2BAA MCHK ∗ ∗ L2DIRTYI ∗ ∗ L2DIRTYO CKSTPI ∗ ∗ L2DOE CKSTPO ∗ L2DWE1 HALTED (N/C) ∗ ∗ L2HIT TLBISYNC L2TALE TBEN ∗ ∗ L2TALOE SUSPEND ∗...

-

Page 119: Floppy/Led Connector J4

Connector Pin Assignments Floppy/LED Connector J4 A 50-pin high-density connector (J4 on the base board) supplies the interface between the base board and an optional external floppy disk drive. In addition to the the disk drive control signals, a set of 16 lines is available to drive an external LED array. -

Page 120: Pci Expansion Connector J5

Common Connectors PCI Expansion Connector J5 The MVME2603/2604 has provision for stacking a PMC carrier board on the base board for additional PCI expansion. A 114-pin connector (J5 on the base board) supplies the interface between the MVME2603/2604 and the carrier board. The pin assignments are listed in the following table. - Page 121 Connector Pin Assignments Table 4-4. PCI Expansion Connector (Continued) AD19 AD18 AD21 AD20 AD23 AD22 AD25 AD24 AD27 AD26 AD29 AD28 AD31 AD30 PAR64 Reserved ∗ ∗ CBE5 CBE4 ∗ ∗ CBE7 CBE6 AD33 AD32 AD35 AD34 AD37 AD36 AD39 AD39 AD41 AD40...

-

Page 122: Keyboard And Mouse Connectors J6, J8

Common Connectors Keyboard and Mouse Connectors J6, J8 The MVME2603/2604 has two 6-pin circular DIN connectors located on the front panel for the keyboard (J6) and mouse (J8). The pin assignments for those connectors are listed in the following two tables. -

Page 123: Table 4-7. Dram Mezzanine Connector

Connector Pin Assignments Table 4-7. DRAM Mezzanine Connector ∗ ∗ A_RAS A_CAS ∗ ∗ B_RAS B_CAS ∗ ∗ C_RAS C_CAS ∗ ∗ D_RAS D_CAS ∗ ∗ ∗ ∗ ∗ ∗ ROMACS ROMBCS RAMAEN RAMBEN RAMCEN EN5VPWR RAL0 RAL1 RAL2 RAL3 RAL4 RAL5 RAL6... - Page 124 Common Connectors Table 4-7. DRAM Mezzanine Connector (Continued) RDL30 RDL31 RDL32 RDL33 RDL34 RDL35 RDL36 RDL37 RDL38 RDL39 RDL40 RDL41 RDL42 RDL43 RDL44 RDL45 RDL46 RDL47 RDL48 RDL49 RDL50 RDL51 RDL52 RDL53 RDL54 RDL55 RDL56 RDL57 RDL58 RDL59 RDL60 RDL61 RDL62 RDL63 CDL0...

-

Page 125: Pci Mezzanine Card Connectors

Connector Pin Assignments Table 4-7. DRAM Mezzanine Connector (Continued) RDU34 RDU35 RDU36 RDU37 RDU38 RDU39 RDU40 RDU41 RDU42 RDU43 RDU44 RDU45 RDU46 RDU47 RDU48 RDU49 RDU50 RDU51 RDU52 RDU53 RDU54 RDU55 RDU56 RDU57 RDU58 RDU59 RDU60 RDU61 RDU62 RDU63 CDU0 CDU1 CDU2 CDU3... -

Page 126: Table 4-8. Pci Mezzanine Card Connector

Common Connectors Table 4-8. PCI Mezzanine Card Connector ∗ Ð12V +12V TRST ∗ PMCINTA ∗ ∗ PMCINTB PMCINTC PMC2TDO ∗ PMC1P Not Used ∗ PMCINTD Not Used Not Used Not Used Not Used Pull-up +3.3V ∗ PCICLK4 PCIRST Pull-down ∗ PMC1GNT +3.3V Pull-down... -

Page 127: Vmebus Connector P1

4Connector Pin Assignments Connector Pin Assignments Table 4-8. PCI Mezzanine Card Connector (Continued) Not Used PMCIO0 PMCIO1 ∗ CBE7 PMCIO2 PMCIO3 ∗ ∗ CBE6 CBE5 PMCIO4 PMCIO5 ∗ CBE4 PMCIO6 PMCIO7 PAR64 PMCIO8 PMCIO9 AD63 AD62 PMCIO10 PMCIO11 AD61 PMCIO12 PMCIO13 AD60 PMCIO14... -

Page 128: Table 4-9. Vmebus Connector P1

MVME2603/2604 Connectors Table 4-9. VMEbus Connector P1 Row Z Row A Row B Row C Row D ∗ Not Used VBBSY Not Used ∗ VBCLR ∗ Not Used VACFAIL VD10 Not Used ∗ VBGIN0 VD11 Not Used ∗ Not Used VBGOUT0 VD12 Not Used... -

Page 129: Mvme712M-Compatible Versions

Connector Pin Assignments MVME712M-Compatible Versions The following tables summarize the pin assignments of connectors that are specific to MVME2603/2604 modules configured for use with MVME712M transition modules. VMEbus Connector P2 (MVME712M I/O Mode) Two 160-pin connectors (P1 and P2) supply the interface between the base board and the VMEbus. -

Page 130: Table 4-10. Vmebus Connector P2 (Mvme712M I/O Mode)

MVME2603/2604 Connectors Table 4-10. VMEbus Connector P2 (MVME712M I/O Mode) Row Z Row A Row B Row C Row D ∗ ∗ SDB8 SDB0 P2C1 PMCIO0 ∗ SDB1 P2C2 PMCIO1 ∗ ∗ ∗ SDB9 SDB2 RETRY P2C3 PMCIO2 ∗ SDB3 VA24 P2C4 PMCIO3... -

Page 131: Table 4-11. Scsi Connector (Mvme712M)

Connector Pin Assignments Table 4-11. SCSI Connector (MVME712M) DB00∗ DB01∗ DB02∗ DB03∗ DB04∗ DB05∗ DB06∗ DB07∗ DBP∗ Reserved TERMPWR ATN∗ BSY∗ ACK∗ RST∗ MSG∗ SEL∗ D/C∗ REQ∗ O/I∗ 4-19... -

Page 132: Serial Ports 1-4 (Mvme712M I/O Mode)

MVME2603/2604 Connectors Serial Ports 1-4 (MVME712M I/O Mode) For the MVME2603/2604, the interface for asynchronous ports 1 and 2 and for synchronous/asynchronous ports 3 and 4 is implemented with four EIA-232-D DB25 connectors (J7-J10) located on the front panel of the MVME712M transition module. The pin assignments for serial ports 1-4 on the MVME712M are listed in the following table. -

Page 133: Parallel Connector (Mvme712M I/O Mode)

Connector Pin Assignments Parallel Connector (MVME712M I/O Mode) Both versions of the base board provide parallel I/O connections. For MVME712M-compatible base boards, the parallel interface is implemented with a 36-pin Centronics-type socket connector located on the MVME712M transition module. The pin assignments are listed in the following table. -

Page 134: Ethernet Aui Connector

MVME2603/2604 Connectors Ethernet AUI Connector The MVME2603/2604 provides both AUI and 10Base-T/100Base- TX LAN connections. For MVME712M-compatible base boards, the LAN interface is an AUI connection implemented with a DB15 connector (J6) located on the MVME712M transition module. The pin assignments are listed in the following table. Table 4-14. -

Page 135: Mvme761-Compatible Versions

Connector Pin Assignments MVME761-Compatible Versions The following tables summarize the pin assignments of connectors that are specific to MVME2603/2604 modules configured for use with MVME761 transition modules. VMEbus Connector P2 (MVME761 I/O Mode) Two 160-pin connectors (P1 and P2) supply the interface between the base board and the VMEbus. -

Page 136: Table 4-15. Vmebus Connector P2 (Mvme761 I/O Mode)

MVME2603/2604 Connectors Table 4-15. VMEbus Connector P2 (MVME761 I/O Mode) Row Z Row A Row B Row C Row D ∗ ∗ SDB8 SDB0 RDÐ (10/100) PMCIO0 ∗ SDB1 RD+ (10/100) PMCIO1 ∗ ∗ ∗ SDB9 SDB2 RETRY TDÐ (10/100) PMCIO2 ∗... -

Page 137: Serial Ports 1 And 2 (Mvme761 I/O Mode)

Connector Pin Assignments Serial Ports 1 and 2 (MVME761 I/O Mode) The MVME2603/2604 provides both asynchronous (ports 1 and 2) and synchronous/asynchronous (ports 3 and 4) serial connections. For the MVME761-compatible versions of the base board, the asynchronous interface is implemented with a pair of DB9 connectors ( ) located on the MVME761 transition COM1... -

Page 138: Serial Ports 3 And 4 (Mvme761 I/O Mode)

MVME2603/2604 Connectors Serial Ports 3 and 4 (MVME761 I/O Mode) For MVME761-compatible versions of the base board, the synchronous/asynchronous interface for ports 3 and 4 is implemented with a pair of HD26 connectors (J7 and J8) located on the front panel of the transition module. The pin assignments for serial ports 3 and 4 are listed in the following table. -

Page 139: Parallel Connector (Mvme761 I/O Mode)

Connector Pin Assignments Parallel Connector (MVME761 I/O Mode) Both versions of the base board provide parallel I/O connections. For MVME761-compatible models, the parallel interface is implemented with an IEEE P1284 36-pin connector (J10) located on the MVME761 transition module. The pin assignments are listed in the following table. -

Page 140: Ethernet 10Base-T/100Base-Tx Connector

MVME2603/2604 Connectors Ethernet 10Base-T/100Base-TX Connector The MVME2603/2604 provides both AUI and 10Base-T/100Base- TX LAN connections. For MVME761-compatible base boards, the LAN interface is a 10Base-T/100Base-TX connection implemented with a standard RJ45 socket located on the MVME761 transition module. The pin assignments are listed in the following table. Table 4-19. -

Page 141: Overview

5PPCBug Overview The PowerPC debugger, PPCBug, is a powerful evaluation and debugging tool for systems built around Motorola PowerPC microcomputers. Facilities are available for loading and executing user programs under complete operator control for system evaluation. The PowerPC debugger provides a high degree of functionality and user friendliness, and yet stresses portability and ease of maintenance. -

Page 142: Memory Requirements

GO), then control may or may not return to PPCBug, depending on the outcome of the user program. The PPCBug is similar to previous Motorola firmware debugging packages (e.g., MVME147Bug, MVME167Bug, MVME187Bug), with differences due to microprocessor architectures. These are... -

Page 143: Using The Debugger

PPCBug Using the Debugger PPCBug is command-driven; it performs its various operations in response to commands that you enter at the keyboard. When the PPC1-Bug prompt appears on the screen, the debugger is ready to accept debugger commands. When the PPC1-Diag prompt appears on the screen, the debugger is ready to accept diagnotics commands. -

Page 144: Debugger Commands

Using the Debugger Debugger Commands The individual debugger commands are listed in the following table. The commands are described in detail in the PPCBug Firmware Package UserÕs Manual, Chapter 2 Note You can list all the available debugger commands by entering the Help (HE) command alone. - Page 145 PPCBug Table 5-1. Debugger Commands (Continued) Command Description FORKWR Fork Idle MPU with Registers Go Direct (Ignore Breakpoints) GEVBOOT Global Environment Variable Boot GEVDEL Global Environment Variable Delete GEVDUMP Global Environment Variable(s) Dump GEVEDIT Global Environment Variable Edit GEVINIT Global Environment Variable Initialization GEVSHOW Global Environment Variable(s) Display Go to Next Instruction Go Execute User Program...

- Page 146 Using the Debugger Table 5-1. Debugger Commands (Continued) Command Description Memory Write Automatic Network Boot Nap MPU Network Boot Operating System, Halt Network Boot Operating System NIOC Network I/O Control NIOP Network I/O Physical NIOT Network I/O Teach (ConÞguration) NPING Network Ping Offset Registers Display/Modify Printer Attach...

- Page 147 PPCBug Table 5-1. Debugger Commands (Continued) Command Description Terminal Attach TIME Display Time and Date Transparent Mode Trace to Temporary Breakpoint Verify S-Records Against Memory Revision/Version Display Write Loop Although a command to allow the erasing and reprogramming of Flash memory is available to you, keep in mind that reprogramming any portion of Flash Caution memory will erase everything currently contained in...

-

Page 148: Diagnostic Tests

Using the Debugger Diagnostic Tests The individual diagnostic test sets are listed in the following table. The diagnostics are described in the PPC1Bug Diagnostics Manual. Table 5-2. Diagnostic Test Groups Test Set Description Applicability DEC21x40 DECchip 21x40 Ethernet Controller Tests All boards Falcon Falcon ECC Memory Controller Tests... -

Page 149: Overview

6CNFG and ENV Commands Overview You can use the factory-installed debug monitor, PPCBug, to modify certain parameters contained in the PowerPC board's Non- Volatile RAM (NVRAM), also known as Battery Backed-up RAM (BBRAM). The Board Information Block in NVRAM contains various elements concerning operating parameters of the hardware. - Page 150 = “07” System Serial Number = “1463725 ” System Identifier = “Motorola MVME2600” License Identifier = “12345678 “ The parameters that are quoted are left-justified character (ASCII) strings padded with space characters, and the quotes (Ò) are displayed to indicate the size of the string. Parameters that are not quoted are considered data strings, and data strings are right- justified.

-

Page 151: Env - Set Environment

CNFG and ENV Commands ENV - Set Environment Use the ENV command to view and/or configure interactively all PPCBug operational parameters that are kept in Non-Volatile RAM (NVRAM). Refer to the PPCBug Firmware Package User's Manual for a description of the use of ENV. Additional information on registers in the Universe ASIC that affect these parameters is contained in your PowerPC board programmerÕs reference guide. - Page 152 ENV - Set Environment Remote Start Method Switch [G/M/B/N] = B? The Remote Start Method Switch is used when the MVME2600/MVME3600/MVME4600 is cross-loaded from another VME-based CPU, to start execution of the cross-loaded program. Use the Global Control and Status Register to pass and start execution of the cross-loaded program.

- Page 153 CNFG and ENV Commands Network PReP-Boot Mode Enable [Y/N] = N? Enable PReP-style network booting (same boot image from a network interface as from a mass storage device). Do not enable PReP-style network booting. (Default) Negate VMEbus SYSFAIL* Always [Y/N] = N? ∗...

- Page 154 ENV - Set Environment NVRAM Bootlist (GEV.fw-boot-path) Boot Enable [Y/N] = N? Give boot priority to devices deÞned in the fw- boot-path global environment variable (GEV). Do not give boot priority to devices listed in the fw-boot-path GEV. (Default) Note When enabled, the GEV (Global Environment Variable) boot takes priority over all other boots, including Autoboot and Network Boot.

- Page 155 CNFG and ENV Commands Auto Boot Scan Enable [Y/N] = Y? If Autoboot is enabled, the Autoboot process attempts to boot from devices speciÞed in the scan list (e.g., FDISK/CDROM/TAPE/HDISK (Default) If Autoboot is enabled, the Autoboot process uses the Controller LUN and Device LUN to boot.

- Page 156 ENV - Set Environment Auto Boot Abort Delay = 7? The time in seconds that the Autoboot sequence will delay before starting the boot. The purpose for the delay is to allow you the option of stopping the boot by use of the key.

- Page 157 CNFG and ENV Commands ROM Boot Direct Ending Address = FFFFFFFC? The last location tested when PPCBug searches for a ROMboot module. (Default = $FFFFFFFC) Network Auto Boot Enable [Y/N] = N? The Network Auto Boot (NETboot) function is enabled. The NETboot function is disabled.

- Page 158 ENV - Set Environment If you use the NIOT debugger command, these parameters need to be saved somewhere in the offset range $00001000 through $000016F7. The NIOT Caution parameters do not exceed 128 bytes in size. The setting of this ENV pointer determines their location. If you have used the same space for your own program information or commands, they will be overwritten and lost.

- Page 159 CNFG and ENV Commands This is the value programmed into the MPC105 ÒROMFALÓ Þeld (Memory Control ConÞguration Register 8: bits 23-27) to indicate the number of clock cycles used in accessing the ROM. The lowest allowable ROMFAL setting is $00; the highest allowable is $1F.

-

Page 160: Conþguring The Vmebus Interface

ENV - Set Environment L2 Cache Parity Enable [On-Detection/Always/Never - O/A/N] = O? L2 Cache parity is enabled upon detection. (Default) L2 Cache parity is always enabled. L2 Cache parity is never enabled. PCI Interrupts Route Control Registers (PIRQ0/1/2/3) = 0A0B0E0F? Initializes the PIRQx (PCI Interrupts) route control registers in the IBC (PCI/ISA bus bridge controller). - Page 161 CNFG and ENV Commands PCI Slave Image 0 Bound Address Register = 00000000? The conÞgured value is written into the LSI0_BD register of the Universe chip. PCI Slave Image 0 Translation Offset = 00000000? The conÞgured value is written into the LSI0_TO register of the Universe chip.

- Page 162 ENV - Set Environment PCI Slave Image 3 Control = C0400000? The conÞgured value is written into the LSI3_CTL register of the Universe chip. PCI Slave Image 3 Base Address Register = 2FFF0000? The conÞgured value is written into the LSI3_BS register of the Universe chip.

- Page 163 CNFG and ENV Commands The conÞgured value is written into the VSI1_BS register of the Universe chip. VMEbus Slave Image 1 Bound Address Register = 00000000? The conÞgured value is written into the VSI1_BD register of the Universe chip. VMEbus Slave Image 1 Translation Offset = 00000000? The conÞgured value is written into the VSI1_TO register of the Universe chip.

- Page 164 ENV - Set Environment The conÞgured value is written into the VSI3_TO register of the Universe chip. PCI Miscellaneous Register = 10000000? The conÞgured value is written into the LMISC register of the Universe chip. Special PCI Slave Image Register = 00000000? The conÞgured value is written into the SLSI register of the Universe chip.

-

Page 165: Motorola Computer Group Documents

VME712MA/IH MVME761 Transition Module Installation and Use VME761A/IH Notes Although not shown in the above list, each Motorola Computer Group manual publication number is suffixed with characters that represent the revision level of the document, such as Ò/xx2Ó (the second revision of a manual);... -

Page 166: Manufacturersõ Documents

Table A-2. Manufacturers’ Documents Publication Document Title and Source Number PowerPC 603 RISC Microprocessor Technical Summary MPC603/D Literature Distribution Center for Motorola Telephone: (800) 441-2447 FAX: (602) 994-6430 or (303) 675-2150 E-mail: ldcformotorola@hibbertco.com PowerPC 603 RISC Microprocessor UserÕs Manual MPC603UM/AD... - Page 167 Table A-2. Manufacturers’ Documents (Continued) Publication Document Title and Source Number PowerPC 604 RISC Microprocessor UserÕs Manual MPC604UM/AD Literature Distribution Center for Motorola Telephone: (800) 441-2447 FAX: (602) 994-6430 or (303) 675-2150 E-mail: ldcformotorola@hibbertco.com IBM Microelectronics MPR604UMU-01 Mail Stop A25/862-1...

- Page 168 ManufacturersÕ Documents Table A-2. Manufacturers’ Documents (Continued) Publication Document Title and Source Number DECchip 21140 PCI Fast Ethernet LAN Controller EC-QC0CA-TE Hardware Reference Manual Digital Equipment Corporation Maynard, Massachusetts DECchip Information Line Telephone (United States and Canada): 1-800-332-2717 TTY (United States only): 1-800-332-2515 Telephone (outside North America): +1-508-568-6868 PC87308VUL ( Super I/O Enhanced Sidewinder Lite) Floppy Disk...

- Page 169 Related Documentation Table A-2. Manufacturers’ Documents (Continued) Publication Document Title and Source Number Z8536 CIO Counter/Timer and Parallel I/O Unit DC-8319-00 Product SpeciÞcation and UserÕs Manual ® (in Z8000 Family of Products Data Book) Zilog, Inc. 210 East Hacienda Ave., mail stop C1-0 Campbell, California 95008-6600 Telephone: (408) 370-8016 FAX: (408) 370-8056...

-

Page 170: Related Speciþcations

Related Specifications Related Specifications For additional information, refer to the following table for related specifications. As an additional help, a source for the listed document is also provided. Please note that in many cases, the information is preliminary and the revision levels of the documents are subject to change without notice. - Page 171 Related Documentation Table A-3. Related Specifications (Continued) Publication Document Title and Source Number IEEE - Common Mezzanine Card SpeciÞcation (CMC) P1386 Draft 2.0 Institute of Electrical and Electronics Engineers, Inc. Publication and Sales Department 345 East 47th Street New York, New York 10017-21633 Telephone: 1-800-678-4333 IEEE - PCI Mezzanine Card SpeciÞcation (PMC) P1386.1 Draft 2.0...

- Page 172 Document Title and Source Number PowerPC Microprocessor Common Hardware Reference Platform: TB338/D A System Architecture (CHRP), Version 1.0 Literature Distribution Center for Motorola Telephone: (800) 441-2447 FAX: (602) 994-6430 or (303) 675-2150 E-mail: ldcformotorola@hibbertco.com APDA, Apple Computer, Inc. P.O. Box 319...

-

Page 173: Speciþcations

Related Documentation Table A-3. Related Specifications (Continued) Publication Document Title and Source Number IEEE Standard for Local Area Networks: Carrier Sense Multiple Access IEEE 802.3 with Collision Detection (CSMA/CD) Access Method and Physical Layer SpeciÞcations Institute of Electrical and Electronics Engineers, Inc. Publication and Sales Department 345 East 47th Street New York, New York 10017-21633... - Page 174 Related Specifications A-10...

-

Page 175: Table B-1. Mvme2603/2604

Specifications Specifications Table B-1 lists the general specifications for MVME2603/2604 base boards. Subsequent sections detail cooling requirements and FCC compliance. A complete functional description of the MVME2603/2604 base boards appears in Chapter 3. Specifications for the optional PCI mezzanines can be found in the documentation for those modules. Table B-1. -

Page 176: Cooling Requirements

Cooling Requirements Cooling Requirements The Motorola MVME2603/2604 family of Single Board Computers is specified, designed, and tested to operate reliably with an incoming air temperature range from 0û to 55û C (32û to 131û F) with forced air cooling of the entire assembly (base board and modules) at a velocity typically achievable by using a 100 CFM axial fan. -

Page 177: Fcc Compliance

Specifications FCC Compliance The MVME2603/2604 Single Board Computer was tested in an FCC-compliant chassis and meets the requirements for Class A equipment. FCC compliance was achieved under the following conditions: Shielded cables on all external I/O ports. Cable shields connected to earth ground via metal shell connectors bonded to a conductive module front panel. - Page 178 FCC Compliance...

-

Page 179: Introduction

CSerial Interconnections Introduction As described in previous chapters of this manual, the MVME2603/2604 serial communications interface has four ports. Two of them are combined synchronous/asynchronous ports; the other two are asynchronous only. Both synchronous and asynchronous ports supply an EIA-232-D DCE/DTE interface via P2 and the MVME712M transition module. -

Page 180: Eia-232-D Connections

EIA-232-D Connections handles both synchronous (SDLC/HDLC) and asynchronous protocols. The hardware supports asynchronous serial baud rates of 110B/s to 38.4KB/s and synchronous baud rates of up to 2.5MB/s. Each port supports the CTS, DCD, RTS, and DTR control signals, as well as the TxD and RxD transmit/receive data signals and TxC/RxC synchronous clock signals. -

Page 181: Table C-1. Eia-232-D Interconnect

Serial Interconnections Table C-1. EIA-232-D Interconnect Signals Signal Signal Name and Description Number Mnemonic Not used. Transmit Data. Data to be transmitted; input to modem from terminal. Receive Data. Data which is demodulated from the receive line; output from modem to terminal. Request To Send. -

Page 182: Interface Characteristics

EIA-232-D Connections Notes 1. A high EIA-232-D signal level is +3 to +15 volts. A low level is −3 to −15 volts. Connecting units in parallel may produce out-of-range voltages and is contrary to specifications. 2. The EIA-232-D interface is intended to connect a terminal to a modem. -

Page 183: Eia-530 Connections

Serial Interconnections cables are permissible provided the total load capacitance measured at the interface point and including signal terminator does not exceed 2500pF. Table C-3. EIA-232-D Interface Receiver Characteristics Value Parameter Unit Minimum Maximum ±25 Input signal voltage 2.25 Input high threshold voltage Input low threshold voltage 0.75 Input hysteresis... -

Page 184: Table C-4. Mvme761 Eia-530 Interconnect Signals

EIA-530 Connections Table C-4. MVME761 EIA-530 Interconnect Signals Signal Signal Name and Description Number Mnemonic Not used. TxD_A Transmit Data (A). Data to be transmitted; output from DTE to DCE. Receive Data (A). Data which is demodulated from the receive line; input from RxD_A DCE to DTE. - Page 185 Serial Interconnections Table C-4. MVME761 EIA-530 Interconnect Signals (Continued) Signal Signal Name and Description Number Mnemonic Data Set Ready (B). Input to DTE from DCE to indicate that the DCE is ready to DSR_B send or receive data. In DCE conÞguration, always true. Data Terminal Ready (B).

-

Page 186: Interface Characteristics

EIA-530 Connections Interface Characteristics In specifying parameters for serial binary data interchange between DTE and DCE devices, the EIA-530 standard assumes the use of balanced lines, except for the Remote Loopback, Local Loopback, and Test Mode lines, which are single-ended. Balanced-line data interchange is generally employed in preference to unbalanced-line data interchange where any of the following conditions prevail: The interconnection cable is too long for effective unbalanced... -

Page 187: Proper Grounding

Serial Interconnections Table C-6. EIA-530 Interface Receiver Characteristics Value Parameter Unit Minimum Maximum ±12 Differential input voltage ±12 Input offset voltage Differential input high threshold voltage −200 Differential input low threshold voltage Input hysteresis Ω Input impedance (−15V < V <... - Page 188 Proper Grounding C-10...

-

Page 189: Introduction

DTroubleshooting CPU Boards: Solving Startup Problems Introduction In the event of difficulty with your CPU board, try the simple troubleshooting steps on the following pages before calling for help or sending the board back for repair. Some of the procedures will return the board to the factory debugger environment. - Page 190 Troubleshooting CPU Boards: Solving Startup Problems Table D-1. Troubleshooting MVME2603/2604 Boards (Continued) Condition Possible Problem Try This: II. There is a A. The keyboard or Recheck the keyboard and/or mouse connections and display on the mouse may be power. terminal, but connected input from the incorrectly.

- Page 191 Introduction Table D-1. Troubleshooting MVME2603/2604 Boards (Continued) Condition Possible Problem Try This: IV. Continued 2. Type in: env;d <CR> This sets up the default parameters for the debugger environment. 3. When prompted to Update Non-Volatile RAM, type in: y <CR> 4.

- Page 192 Troubleshooting CPU Boards: Solving Startup Problems Table D-1. Troubleshooting MVME2603/2604 Boards (Continued) Condition Possible Problem Try This: V. The debugger is A. No apparent No further troubleshooting steps are required. in system mode problems Ñ and the board troubleshooting autoboots, or is done.

-

Page 193: Glossary

Glossary Abbreviations, Acronyms, and Terms to Know This glossary defines some of the abbreviations, acronyms, and key terms used in this document. An Ethernet implementation in which the physical medium 10Base-5 is a doubly shielded, 50-ohm coaxial cable capable of carrying data at 10 Mbps for a length of 500 meters (also referred to as thicknet). - Page 194 Glossary Application-Specific Integrated Circuit ASIC Attachment Unit Interface Battery Backed-up Random Access Memory BBRAM Having big-endian and little-endian byte ordering bi-endian capability. A byte-ordering method in memory where the address big-endian n of a word corresponds to the most significant byte. In an addressed memory word, the bytes are ordered (left to right) 0, 1, 2, 3, with 0 being the most significant byte.

- Page 195 The Green signals (G-Y) can be extracted by these two signals. Common Hardware Reference Platform (CHRP) A specification published by the Apple, IBM, and Motorola which defines the devices, interfaces, and data formats that make up a CHRP-compliant system using a PowerPC processor.

- Page 196 Glossary Central Processing Unit. The master computer unit in a system. Data Circuit-terminating Equipment. Dynamic Link Library. A set of functions that are linked to the referencing program at the time it is loaded into memory. Direct Memory Access. A method by which a device may read or write to memory directly without processor intervention.

- Page 197 A local area network standard that uses radio frequency Ethernet signals carried by coaxial cables. The DRAM controller chip developed by Motorola for the Falcon MVME2600 and MVME3600 series of boards. It is intended to be used in sets of two to provide the necessary interface between the Power PC60x bus and the 144-bit ECC DRAM (system memory array) and/or ROM/Flash.

- Page 198 Glossary (peripherals) that make up the system. A computing system is normally spoken of as having two major components: hardware and software. Hardware Conformance Test. A test used to ensure that both hardware and software conform to the Windows NT interface.

- Page 199 Motorola Computer Group Modified Frequency Modulation Musical Instrument Digital Interface. The standard format MIDI for recording, storing, and playing digital music. Multimedia Personal Computer MotorolaÕs component designation for the PowerPC 601 MPC601 microprocessor. MotorolaÕs component designation for the PowerPC 603 MPC603 microprocessor.

- Page 200 Glossary A video system in which every pixel is refreshed during non-interlaced every vertical scan. A non-interlaced system is normally more expensive than an interlaced system of the same resolution, and is usually said to have a more pleasing appearance. A memory in which the data content is maintained whether nonvolatile memory the power supply is connected or not.

- Page 201 (branch units, fixed-point units, and floating-point units), where they can execute concurrently, but finish out of order. PowerPC is used by Motorola, Inc. under license from IBM. The first implementation of the PowerPC family of PowerPC 601™...

- Page 202 The PowerPC-to-PCI local bus bridge chip developed by Raven Motorola for the MVME2600 and MVME3600 series of boards. It provides the necessary interface between the PowerPC 60x bus and the PCI bus, and acts as interrupt controller.

- Page 203 Glossary The three separate color signals: Red, Green, and Blue. Used with color displays, an interface that uses these three color signals as opposed to an interface used with a monochrome display that requires only a single signal. Both digital and analog RGB interfaces exist. See Reduced-Instruction-Set Computer (RISC).

- Page 204 Glossary The term used to describe any single program or group of software programs, languages, operating procedures, and documentation of a computer system. A computing system is normally spoken of as having two major components: hardware and software. Software is the real interface between the user and the computer.

- Page 205 Glossary Video Electronics Standards Association (or VL bus). An VESA (bus) internal interconnect standard for transferring video information to a computer display system. Video Graphics Array (IBM). The third and most common monitor standard used today. It provides up to 256 simultaneous colors and a screen resolution of 640 x 480 pixels.

- Page 206 Glossary GL-14...

- Page 207 Index configuration, transition module serial port 1-17, 1-27 abbreviations, acronyms, and terms to configure know GL-1 PPC1Bug parameters Abort (interrupt) signal 3-18 VMEbus interface 6-12 abort (interrupt) signal Configure Board Information Block adapter board, P2 1-15, 1-25, 1-45, 1-48, 3-6, 3-23 (CNFG) adapter, P2 connector pin assignments...

- Page 208 Index processor/memory domain 2-14 keyboard/mouse 3-12, 4-10 VMEbus domain 2-15 parallel 3-11 ENV command PCI bus environmental parameters SCSI ESD precautions 1-35 serial 3-11, 3-15, C-1 Ethernet 1-52, 3-20 VMEbus station address interrupt architecture, MVME2603/2604 2-11 interrupt signals 3-18 interrupt support 2-10 Falcon memory controller chip set 2-5, 2-10,...

- Page 209 Index ROMNAL 6-11 NETboot enable Network Auto Boot enable SCSI Non-Volatile RAM (NVRAM) 6-1, 6-3 cabling 1-45 interface termination operating parameters terminator power 1-52, 3-20, 3-21 SCSI bus serial communications interface 3-15, C-1 P2 adapter serial interface 3-11 for MVME761 1-34 serial interface modules (SIMs) 3-25...

- Page 210 Index uppercase using the board VME64 bus extension VMEbus address/data configurations 1-51 Universe ASIC and VMEbus interface 6-12 Winbond PCI/ISA bus bridge controller 2-9, 3-12 IN-4...